Abstract

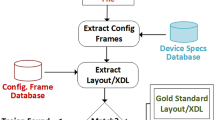

This paper presents an innovative way to deploy Bitstream Intellectual Property (BIP) cores. By using standard tools to generate bitstreams for Field Programmable Gate Arrays (FPGAs) and a tool called PARBIT, it is possible to extract a partial bitstream containing a modular component developed on one Virtex FPGA that can be placed or relocated inside another Virtex FPGAs. The methodology to obtain the BIP cores is explained, along with details about PARBIT and Virtex devices.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

VSIA: VSI Alliance Architecture Document. VSI Alliance (1997), Online http://www.-vsi.org/resources/techdocs/vsi-or.pdf

Kalte, H., Porrmann, M., Rückert, U.: A Prototyping Platform for Dynamically Reconfigurable System on Chip Designs. In: IEEE Workshop Heterogeneous reconfigurable Systems on Chip (SoC), Hamburg, Germany (2002)

Lockwood, J.W.: An open platform for development of network processing modules in reprogrammable hardware. In: IEC DesignCon 2001, Santa Clara, CA, pp. WB–19 (2001)

Lockwood, J.W., Turner, J.S., Taylor, D.E.: Field programmable port extender (FPX) for distributed routing and queuing. In: ACM International Symposium on Field Programmable Gate Arrays (FPGA 2000), Monterey, CA, USA, pp. 137–144 (2000)

Blodget, B., James-Roxby, P., Kelle, E., McMillan, S., Sundararajan, P.: A selfreconfiguring platform. In: Y. K. Cheung, P., Constantinides, G.A. (eds.) FPL 2003. LNCS, vol. 2778, pp. 565–574. Springer, Heidelberg (2003)

Horta, E., Lockwood, J.W.: PARBIT: a tool to transform bitfiles to implement partial reconfiguration of field programmable gate arrays (FPGAs). Technical Report WUCS-01-13,Washington University in Saint Louis, Department of Computer Science, July 6 (2001)

Horta, E.L., Lockwood, J.W., Taylor, D.E., Parlour, D.: Using PARBIT to implement Partial Run-Time Reconfigurable Systems. In: 12th International Conference on Field Programmable Logic and Applications, Montpellier, France (2002)

Xilinx, I.: Foundation series user guide (2004), http://toolbox.xilinx.com/docsan/xilinx6/pdf/docs/fsu/fsu.pdf

Horta, E.L., Lockwood, J.W., Taylor, D.E., Parlour, D.: Dynamic hardware plugins in an FPGA with partial run-time reconfiguration. In: Design Automation Conference (DAC), New Orleans, LA (2002)

Lim, D., Peattie, M.: Two Flows for Partial Reconfiguration: Module Based or Small Bit Manipulations. Xilinx XAPP290 (2002)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2004 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Horta, E.L., Lockwood, J.W. (2004). Automated Method to Generate Bitstream Intellectual Property Cores for Virtex FPGAs. In: Becker, J., Platzner, M., Vernalde, S. (eds) Field Programmable Logic and Application. FPL 2004. Lecture Notes in Computer Science, vol 3203. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-540-30117-2_110

Download citation

DOI: https://doi.org/10.1007/978-3-540-30117-2_110

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-22989-6

Online ISBN: 978-3-540-30117-2

eBook Packages: Springer Book Archive