Abstract

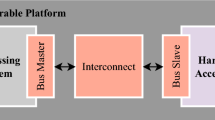

We present in this paper a development method for SOC platforms associating a processor running a RTOS and hardware IP’s. This method is based on encapsulating IP’s for unifying communications and resource sharing between software and hardware tasks. A hardware wrapper that abstracts the IP behaviours through a standard interface and a software encapsulation (the IP Alter Ego) thereby giving access to the Operating System functions are presented. Details about implementing this model on two different FPGA platforms are given.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Chen, Z., Cong, J., Fan, Y., Yang, X., Zhang, Z.: Pilot- A Platform-Based HW/SW Synthesis for FPSoC. In: Workshop on Software support for Reconfigurable systems (2003)

Vanmeerbeeck, G., Schaumont, P., Vernalde, S., Engels, M., Bolsens, I.: Hardware/Software partitioning of embedded system in OCAPI-xl. In: Ninth International Symposium on Hardware/Software Codesign (2000)

Marescaux, T., Mignolet, J.Y., Bartic, A., Moffat, W., Verkest, D., Vernalde, S., Lauwereins, R.: Networks on Chip as Hardware Component of an OS for Reconfigurable Systems. In: Y. K. Cheung, P., Constantinides, G.A. (eds.) FPL 2003. LNCS, vol. 2778, Springer, Heidelberg (2003)

Lyonnard, D., Yoo, S., Baghdadi, A., Jerraya, A.A.: Automatic Generation of Application-Specific Architecture for Heterogeneous Multiprocessor System-on-Chip. In: DAC (2001)

Svarstad, K., Nicolescu, G., Jerraya, A.A.: A Model for Describing Communication between Aggregate Objects in the Specification and Design of Embedded Systems. In: DATE (2001)

Labrosse, J.J.: MicroC/OS-II, The Real-Time Kernel. CMP Books, Lawrence, Kansas 66046, USA (2002)

Blodget, B., McMillan, S., Lysaght, P.: A Lighweight Approach for Embedded Reconfiguration of FPGAs. In: Proceedings of DATE, 399–400 (2003)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2004 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Segard, A., Verdier, F. (2004). SOC and RTOS: Managing IPs and Tasks Communications. In: Becker, J., Platzner, M., Vernalde, S. (eds) Field Programmable Logic and Application. FPL 2004. Lecture Notes in Computer Science, vol 3203. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-540-30117-2_72

Download citation

DOI: https://doi.org/10.1007/978-3-540-30117-2_72

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-22989-6

Online ISBN: 978-3-540-30117-2

eBook Packages: Springer Book Archive