Abstract

Microprocessor design is a considerably complex task. First, microprocessors include many resources that may be configured in different ways. This leads to a time consuming multi-objective optimization problem. Second, currently the designs must take into account not only performance but also power consumption thus making the optimization goal more complex. Third, different types of applications have different demands but producing several different microprocessors would not be cost effective.

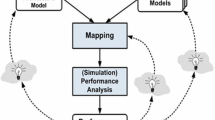

This paper proposes an efficient algorithm to explore the design space: design space navigation. With this algorithm it is possible to obtain optimal configurations by starting from a baseline and “navigating” on the design space. Different configurations tailored for different applications, but derived from the same baseline, are called neighboring configurations. Experimental results show that navigation finds designs that achieve better power-performance efficiency for a fraction of the time required by other design space exploration algorithms. Also, the algorithm is used to obtain four neighboring configurations for four types of applications: multimedia, integer and floating-point scientific, and database workloads. The results showed that the navigation configuration achieves a power-performance improvement of 30% to 118% depending on the workload. Using different workloads for navigation and execution may result in a loss of efficiency of as much as 94%.

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Lefurgy, C., Rajamani, K., Rawson, F., Felter, W., Kristler, M., Keller, T.: Energy Management for Commercial Servers. IEEE Computer 36, 39–48 (2003)

Brooks, D., Bose, P., Schuster, S., Jacobson, H., Kudva, P., Buyuktosunoglu, A., Wellman, J.D., Zyuban, V., Gupta, M., Cook, P.: Power-Aware Microarchitecture: Design and Modeling Challenges for Next-Generation Microprocessors. In: IEEE Micro., pp. 26–44 (2000)

Fornaciari, W., Sciuto, D., Silvano, C., Zaccaria, V.: A Design Framework to Efficiently Explore Energy-Delay Tradeoffs. In: Proceedings of the ninth international symposium on Hardware/software codesign, pp. 260–265. ACM Press, New York (2001)

Palesi, M., Givargis, T.: Multi-Objective Design Space Exploration Using Generic Algorithms. In: Proceedings of the CODES, pp. 67–72 (2002)

Palermo, G., Silvano, C., Valsecchi, S., Zaccaria, V.: A System-Level Methodology for Fast Multi-Objective Design Space Exploration. In: Proceedings of the GLSVLSI, pp. 92–95 (2003)

Agosta, G., Palermo, G., Silvano, C.: Multi-Objective Co-Exploration of Source Code Transformations and Design Space Architectures for Low-Power Embedded Systems. In: Proceedings of the SAC, pp. 891–896 (2004)

Kin, J., Lee, C., Mangione-Smith, W.H., Potkonjak, M.: Power Efficient Mediaprocessors: Design Space Exploration. In: Proceedings of the DAC, pp. 321–326 (1999)

Bahar, R., Albera, G., Manne, S.: Power and Performance Tradeoffs Using Various Caching Strategies. In: Proceedings of the 1998 ISLPED, pp. 64–69. ACM Press, New York (1998)

Brooks, D., Tiwari, V., Martonosi, M.: Wattch: a Framework for Architecturallevel Power Analysis and Optimizations. In: Proceedings of the 27th ISCA, pp. 83–94 (2000)

Conte, T., Menezes, K., Sathaye, S., Toburen, M.: System-Level Power Consumption Modeling and Trade-off Analysis Techniques for Superscalar Processor Design. IEEE Transactions on VLSI Systems 8, 129–137 (2000)

Folegnani, D., González, A.: Energy-Effective Issue Logic. In: Proceedings of the 28th ISCA, pp. 230–239 (2001)

Gonzalez, R., Horowitz, M.: Energy Dissipation in General Purpose Microprocessors. IEEE Journal of Solid-State Circuits 31, 1277–1284 (1996)

Hicks, P., Walnock, M., Owens, R.M.: Analysis of Power Consumption in Memory Hierarchies. In: Proceedings of the ISLPED, pp. 239–242 (1997)

Huang, M., Renau, J., Yoo, S.M., Torrellas, J.: L1 Data Cache Decomposition for Energy Efficiency. In: Proceedings of the ISLPED, pp. 10–15 (2001)

Miyoshi, A., Lefurgy, C., Hensbergen, E.V., Rajamony, R., Rajkumar, R.: Critical Power Slope: Understanding the Runtime Effects of Frequency Scaling. In: Proceedings of the Int’l Conf. on Supercomputing, pp. 35–44 (2002)

Su, C.L., Despain, A.: Cache Design Trade-offs for Power and Performance Optimization: a Case Study. In: Proceedings of the 1995 ISLPD, pp. 63–68. ACM Press, New York (1995)

Zhou, H., Toburen, M., Rotenberg, E., Conte, T.M.: Adaptive Mode Control: A Static-Power Efficient Cache Design. In: Proceedings of the IEEE PACT, pp. 61–72 (2001)

Hughes, C., Srinivasan, J., Adve, S.: Saving Energy with Architectural and Frequency Adaptations for Multimedia Applications. In: Proceedings of the 34th Annual Int’l Symp. on Microarchitecture (MICRO-34), pp. 250–261 (2001)

Unsal, O., Ashok, R., Koren, I., Krishna, C., Moritz, C.: Cool-Cache for Hot Multimedia. In: Proceedings of the 34th Annual Int’l Symp. on Microarchitecture ( MICRO-34), pp. 274–283 (2001)

An, N., Sivasubramaniam, A., Vijaykrishnan, N., Kandemir, M.T., Irwin, M.J., Gurumurthi, S.: Analyzing Energy Behavior of Spatial Access Methods for Memory- Resident Data. The VLDB Journal, 411–420 (2001)

Austin, T., Larson, E., Ernst, D.: SimpleScalar: An Infrastructure for Computer System Modeling. IEEE Computer, 59–67 (2002)

Shivakumar, P., Jouppi, N.: CACTI 3.0: An Integrated Cache Timing, Power, and Area Model. Technical report, Compaq Western Research Laboratory (2001)

Lee, C., Potkonjak, M., Mangione-Smith, W.: MediaBench: A Tool for Evaluating and Synthesizing Multimedia and Communicatons Systems. In: International Symposium on Microarchitecture, pp. 330–335 (1997)

Henning, J.L.: SPEC CPU2000: Measuring CPU Performance in the New Millennium. IEEE Computer 33, 28–35 (2000)

Transaction Processing Performance Council: TPC BenchmarkTM H (Decision Support), Standard Specification (1999)

Barroso, L., Gharachorloo, K., Bugnion, E.: Memory System Characterization of Commercial Workloads. In: Proceedings of the 25th ISCA, pp. 3–14 (1998)

Team, T.T.: In-Memory Data Management for Consumer Transactions: The TimesTen Approach. In: Proceedings of the ACM SIGMOD Conference, pp. 528–529 (1999)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2005 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Trancoso, P. (2005). Design Space Navigation for Neighboring Power-Performance Efficient Microprocessor Configurations. In: Beigl, M., Lukowicz, P. (eds) Systems Aspects in Organic and Pervasive Computing - ARCS 2005. ARCS 2005. Lecture Notes in Computer Science, vol 3432. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-540-31967-2_14

Download citation

DOI: https://doi.org/10.1007/978-3-540-31967-2_14

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-25273-3

Online ISBN: 978-3-540-31967-2

eBook Packages: Computer ScienceComputer Science (R0)