Abstract

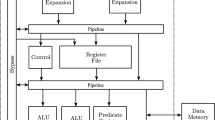

In this paper, we propose a new next generation high-performance micro-architecture based on the combination of simultaneous multithreading and trace processor. By exploiting both Instruction-Level Parallelism and Thread-Level Parallelism, Simultaneous Multithreading Trace Processor can be expected to achieve higher performance than SMT or Trace Processor individual. We describe the organization of SMT Trace Processor architecture and some fundamental techniques. A path-based multiple traces prediction mechanism is also described in the paper.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Hennessy, J.L., Patterson, D.A.: Computer Architecture A Quantitative Approach, 2nd edn. Morgan Kaufmann, San Francisco (1996)

Rotenberg, E., Jacobson, Q., Sazeides, Y., Smith, J.: Trace Processors. In: Proceedings of the 30th International Symposium on Microarchitecture(MICRO-30), December 1997, pp. 138–148 (1997)

Tullsen, D.M., Eggers, S.J., Levy, H.M.: Simultaneous multithreading: Maximizing on-chip parallelism. In: Proceedings of the 22nd Annual International Symposium on Computer Architecture, June 1995, pp. 392–403 (1995)

Rotenberg, E., Bennett, S., Smith, J.E.: Trace cache: a low latency approach to high bandwidth instruction fetching. In: Proceedings of the 29th Annual International Symposium on Micro-architecture, December 1996, pp. 24–35 (1996)

Jacobson, Q., Rotenberg, E., Smith, J.E.: Path-Based Next Trace Prediction. In: Proceedings of the 30th International Symposium on Microarchitecture, December 1997, pp. 14–23 (1997)

Patel, S.J., Evers, M., Patt, Y.N.: Improving Trace Cache Effectiveness with Branch Promotion and Trace Packing. In: Proceedings of the 25th International Symposium on Computer Architecture, Barcelona, Spain (June 1998)

Yeh, T.-Y., Patt, Y.: Two-level Adaptive Branch Prediction. In: proceedings of the 24th International Symposium on Microarchitecture, November 1991, pp. 51–61 (1991)

Franklin, M., Sohi, G.S.: ARB: A hardware mechanism for dynamic reordering of memory references. IEEE Transactions on Computers 45(5), 552–571 (1996)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2003 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Wang, K.F., Ji, Z., Hu, M. (2003). Simultaneous Multithreading Trace Processors. In: Zhou, X., Xu, M., Jähnichen, S., Cao, J. (eds) Advanced Parallel Processing Technologies. APPT 2003. Lecture Notes in Computer Science, vol 2834. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-540-39425-9_10

Download citation

DOI: https://doi.org/10.1007/978-3-540-39425-9_10

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-20054-3

Online ISBN: 978-3-540-39425-9

eBook Packages: Springer Book Archive