Abstract

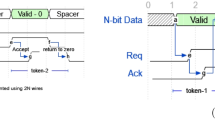

A novel Globally Asynchronous Locally Synchronous (GALS) technique applicable to datapath architectures is presented. It is based on a request-driven operation of locally synchronous blocks. Inactivity of the request line is detected with a special time-out circuitry. When time-out occurs, clocking of the locally synchronous block is handed over to a local ring oscillator. Based on this concept, a practical hardware implementation of an asynchronous wrapper is proposed. The simulation results presented demonstrate the potential and performance of the proposed GALS architecture.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Yun, K.Y., Donohue, R.P.: Pausible Clocking: A first step toward heterogeneous systems. In: Proc. International Conference on Computer Design (ICCD) (October 1996)

Bormann, D.S., Cheoung, P.Y.K.: Asynchronous Wrapper for Heterogeneous Systems. In: Proc. International Conf. Computer Design (ICCD) (October 1997)

Muttersbach, J.: Globally-Asynchronous Locally-Synchronous Architectures for VLSI Systems, Doctor of Technical Sciences Dissertation, ETH Zurich, Switzerland (2001)

Moore, S., et al.: Self Calibrating Clocks for Globally Asynchronous Locally Synchronous System. In: Proc. International Conference on Computer Design (ICCD) (September 2000)

Chapiro, D.M.: Globally-Asynchronous Locally-Synchronous Systems, PhD thesis, Stanford University (October 1984)

Moore, S., et al.: Point to Point GALS interconnect. In: Proc. International Symposium on Asynchronous Circuits and Systems, April 2002, pp. 69–75 (2002)

Yun, K.Y., Dill, D.: Automatic synthesis of extended burst-mode circuits: Part I and II. IEEE Transactions on Computer-Aided Design 18(2), 101–132 (1999)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2003 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Krstić, M., Grass, E. (2003). New GALS Technique for Datapath Architectures. In: Chico, J.J., Macii, E. (eds) Integrated Circuit and System Design. Power and Timing Modeling, Optimization and Simulation. PATMOS 2003. Lecture Notes in Computer Science, vol 2799. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-540-39762-5_18

Download citation

DOI: https://doi.org/10.1007/978-3-540-39762-5_18

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-20074-1

Online ISBN: 978-3-540-39762-5

eBook Packages: Springer Book Archive