Abstract

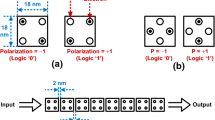

Discrete devices speeding up is the actual aspect of logic design. The combinational circuit delay essentially depends on the number of levels involved. To reduce the number of circuit levels as well as its delay a multiplexing-based technique is proposed. At first, a given Boolean function (more precisely, its SOP) is represented in partially orthogonalized form: SOP=k 1 (SOP 1)+k 2(SOP 2)+ ... +k r (SOP r ), where the factor-products k 1,...,k r are orthogonal to each other, and k 1 +k 2 + ... +k r ≡ 1. Then this Boolean function is implemented through multiplexing of the subcircuits corresponding to SOP i , i =1, ..., r. Switching of these subcircuits carries out by three-state gates, controlled by mutually orthogonal factor-products k i , i =1, ..., r. The decrease of delay is achieved by calculating of the SOP i and k i in parallel and thanks to an ordinary wired joint of the subcircuit outputs instead of using the multi-input OR. The method suggested is focused on the speeding up of some critical circuit path in conditions then wired OR is impermissible.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Zakrevskij, A.: Combinatorial Problems over Logical Matrices in Logic Design and Artificial Intelligence. Revista do DETUA, Janeiro 2(2), 261–268 (1998)

Zakrevskij, A.D.: Logic Design of Cascade Circuits. Science, Moscow, 416 (1981) (In Russian)

Badulin, S.S. (ed.): Computer-Aided Design of Digital Devices. Radio & Communications, Moscow, p. 240 (1981) (In Russian)

Tomachev, V.: The PLD-Implementation of Boolean Function Characterized by Minimum Delay. In: Hartenstein, R.W., Keevallik, A. (eds.) FPL 1998. LNCS, vol. 1482, pp. 481–484. Springer, Heidelberg (1998)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 1999 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Tomashau, V.F. (1999). Logic Circuit Speeding up through Multiplexing. In: Lysaght, P., Irvine, J., Hartenstein, R. (eds) Field Programmable Logic and Applications. FPL 1999. Lecture Notes in Computer Science, vol 1673. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-540-48302-1_50

Download citation

DOI: https://doi.org/10.1007/978-3-540-48302-1_50

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-66457-4

Online ISBN: 978-3-540-48302-1

eBook Packages: Springer Book Archive