Abstract

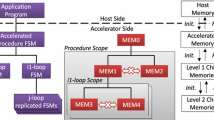

This paper describes memory access optimization in the context of pipeline vectorization, a method for synthesizing hardware pipe- lines in reconfigurable systems from software program loops. Since many algorithms for reconfigurable coprocessors are I/O bound, the throughput of the coprocessor is determined by the external memory accesses. Thus access optimizations directly improve the system’s performance. Two kinds of optimizations have been studied. First, we consider methods for reducing the number of accesses based on saving frequently-used data in on-chip storage. In particular, recent FPGAs provide on-chip RAM which can be used for this purpose. We present RAM inference, a technique which automatically extracts small on-chip RAMs to reduce external memory accesses. Second, we aim to minimize the time spent on external accesses by scheduling as many accesses in parallel as possible. This optimization only applies to architectures with multiple memory banks. We present a technique which allocates program arrays to memory banks, thereby minimizing the overall access time.

This work is supported by a European Union training project financed by the Commission in the TMR programme, the UK Engineering and Physical Sciences Research Council, Embedded Solutions Ltd., and Xilinx Inc.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Weinhardt, M., Luk, W.: Pipeline vectorization for reconfigurable systems. In: Proc. FCCM 1999. IEEE Computer Society Press, Los Alamitos (1999)

Haug, G., Rosenstiel, W.: Reconfigurable hardware as shared resource in multipurpose computers. In: Proc. FPL 1998. Springer, Heidelberg (1998)

Gokhale, M.B., Stone, J.M.: NAPA C: compiling for a hybrid RISC/FPGA architecture. In: Proc. FCCM 1998. IEEE Computer Society Press, Los Alamitos (1998)

Weinhardt, M.: Compilation and pipeline synthesis for reconfigurable architectures. In: Reconfigurable Architectures Workshop RAW 1997 (1997)

Weinhardt, M.: Übersetzungsmethoden für strukturprogrammierbare Rechner (Compilation techniques for structurally programmable computers, in German). PhD thesis, Universität Karlsruhe (July 1997)

Guccione, S.A., Gonzalez, M.J.: A data-parallel programming model for reconfigurable architectures. In: Proc. FCCM 1993. IEEE Computer Society Press, Los Alamitos (1993)

Nisbet, S., Guccione, S.A.: The XC6200DS development system. In: Glesner, M., Luk, W. (eds.) FPL 1997. LNCS, vol. 1304. Springer, Heidelberg (1997)

Buell, D.A., Arnold, J.M., Kleinfelder, W.J.: Splash 2 - FPGAs in a Custom Computing Machine. IEEE Computer Society Press, Los Alamitos (1996)

Embedded Solutions Limited. RC1000-PP Product Information Sheet, http://www.embedded-solutions.ltd.uk/ProdApp/RC1000PP.htm

Gokhale, M.B., Stone, J.M.: Automatic allocation of arrays to memories in FPGA processors with multiple memory banks. In: Proc. FCCM 1999. IEEE Computer Society Press, Los Alamitos (1999)

Myler, H.R., Weeks, A.R.: Computer Imaging Recipes in C. Prentice Hall, Englewood Cliffs (1993)

Berkelaar, M.: Unix manual page of lp_solve. Eindhoven University of Technology, Design Automation Section (1992)

Weinhardt, M.: Integer programming for partitioning in software oriented codesign. In: Proc. FPL 1995, Springer, Heidelberg (1995)

Embedded Solutions Limited. Handel-C Reference Manual (1998)

The Stanford SUIF Compiler Group. Homepage, http://suif.stanford.edu

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 1999 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Weinhardt, M., Luk, W. (1999). Memory Access Optimization and RAM Inference for Pipeline Vectorization. In: Lysaght, P., Irvine, J., Hartenstein, R. (eds) Field Programmable Logic and Applications. FPL 1999. Lecture Notes in Computer Science, vol 1673. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-540-48302-1_7

Download citation

DOI: https://doi.org/10.1007/978-3-540-48302-1_7

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-66457-4

Online ISBN: 978-3-540-48302-1

eBook Packages: Springer Book Archive