Abstract

This paper presents a novel high-level analytical approach to estimate logic power consumption of multipliers implemented in FPGAs in the presence of glitching and correlation. The proposed methodology is based on: 1) an analytical model for the switching activity of the component, and 2) a structural analysis of the FPGA implementation of the component. The complete model is parameterized in terms of complexity factors such as word-lengths and signal statistics of the operands. It also accounts for the glitching introduced by the component. Compared to the other power estimation methods, the number of circuit simulations needed for characterizing the power model of the component is highly reduced. The accuracy of the model is within 10% of low-level power estimates given by the tool XPower and it achieves better performance than other proposed high-level approaches.

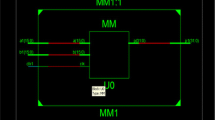

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Andraka Consulting Group: Multiplication in FPGAs, available at http://www.fpga-guru.com/multipli.htm

Clarke, J.A., Gaffar, A.A., Constantinides, G.A.: Parameterized logic power consumption models for FPGA-based arithmetic. In: Proc. FPL, pp. 626–629 (2005)

Chou, T., Roy, K., Prasad, S.: Estimation of Circuit Activity Considering Signal Correlations and Simulteneous Switching. In: Proc. of the 1994 IEEE/ACM Int. Conference on Computer-aided Design, pp. 300–303. ACM Press, New York (1994)

GNU MP library, available at http://www.swox.com/gmp/

Gupta, S., Najm, F.N.: Power Modeling for High Level Power Estimation. IEEE Trans. VLSI Syst. 8, 18–29 (2000)

Landman, P., Rabaey, J.: Architectural Power Analysis: The dual bit type method. IEEE Trans. On VLSI Systems 3(2), 173–187 (1995)

Ramprasad, S., Shanbhag, N.R., Hajj, I.N.: Analytical Estimation of Signal Transition Activity from Word-Level Statistics. IEEE Trans. On Computer-Aided Design of Integrated Circuits and Systems 16(7), 718–733 (1997)

Satyanarayana, J.H., Parhi, K.K.: Theoretical Analysis of Word-Level Switching Activity in the Presence of Glitching and Correlation. IEEE Trans. On VLSI Systems 8(2), 148–159 (2000)

Shang, L., Jha, N.K.: High-level Power Modeling of CPLDs and FPGAs. In: Proc. Of the Int. Conf. on Comp. Design, pp. 46–53. IEEE Computer Society Press, Los Alamitos (2001)

Xilinx Inc., http://www.xilinx.com

Zhong, L., Jha, N.K.: Interconnect-aware High-level Synthesis for Low Power. In: IEEE/ACM International Conf. on CAD, Nov. 2002, pp. 110–117. ACM Press, New York (2002)

Author information

Authors and Affiliations

Editor information

Rights and permissions

Copyright information

© 2007 Springer Berlin Heidelberg

About this paper

Cite this paper

Jevtic, R., Carreras, C., Caffarena, G. (2007). Switching Activity Models for Power Estimation in FPGA Multipliers. In: Diniz, P.C., Marques, E., Bertels, K., Fernandes, M.M., Cardoso, J.M.P. (eds) Reconfigurable Computing: Architectures, Tools and Applications. ARC 2007. Lecture Notes in Computer Science, vol 4419. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-540-71431-6_19

Download citation

DOI: https://doi.org/10.1007/978-3-540-71431-6_19

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-71430-9

Online ISBN: 978-3-540-71431-6

eBook Packages: Computer ScienceComputer Science (R0)