Abstract

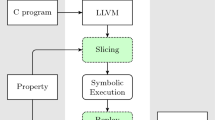

SVtL is the core of a slicing-based verification environment for UML statechart models. We present an overview of the SVtL software architecture. Special attention is paid to the slicing approach. Slicing reduces the complexity of the verification approach, based on removing pieces of the model that are not of interest during verification. In [18] a slicing algorithm has been proposed for statecharts, but it was not able to handle orthogonal regions efficiently. We optimize this algorithm by removing false dependencies, relying on the broadcasting mechanism between different parts of the statechart model.

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Michelle, L.: Crane and Juergen Dingel. On the Semantics of UML State Machines: Categorization and Comparison. Technical Report 2005, School of Computing Queen’s University Kingston, Ontario, Canada 2005-501 (2005)

David, A., Deneux, J., d’Orso, J.: A Formal Semantics for UML Statecharts. Technical Report 2003-010, Uppsala University (2003)

Dwyer, M.B., Avrunin, G.S., Corbett, J.C.: Patterns in Property Specifications for Finite-State Verification. In: ICSE ’99: Proceedings of the 21st international conference on Software engineering, Los Angeles, California, United States, pp. 411–420. IEEE Computer Society Press, Los Alamitos (1999)

Gnesi, S.: Model Checking of Embedded Systems (January 2003)

Encarnación Beato Gutiérrez, M., Barrio-Solórzano, M., Cuesta Quintero, C.E., de la Fuente, P.: UML Automatic Verification Tool with Formal Methods. Electr. Notes Theor. Comput. Sci. 127(4), 3–16 (2005)

Jacobs, B.: Many-Sorted Coalgebraic Modal Logic: a Model-Theoretic Study. ITA 35(1), 31–59 (2001)

Johnson, S.D.: Formal Methods in Embedded Design. Computer 36(11), 104–106 (2003)

Kahlon, V., Gupta, A.: An Automata-Theoretic Approach for Model Checking Threads for LTL properties. In: LICS ’06: Proceedings of the 21st Annual IEEE Symposium on Logic in Computer Science, Washington, DC, USA, pp. 101–110. IEEE Computer Society Press, Los Alamitos (2006)

Lamport, L.: Time, Clocks, and the Ordering of Events in a Distributed System. Commun. ACM 21(7), 558–565 (1978), doi:10.1145/359545.359563

Van Langenhove, S.: Towards the Correctness of Software Behavior in UML: A Model Checking Approach Based on Slicing. Ph.D. Thesis UGent (May 2006)

Latella, D., Majzik, I., Massink, M.: Towards a Formal Operational Semantics of UML Statechart Diagrams. In: Proc. FMOODS’99, IFIP TC6/WG6.1 Third International Conference on Formal Methods for Open Object-Based Distributed Systems, Florence, Italy, February 15-18, 1999, pp. 331–347. Kluwer Academic Publishers, Dordrecht (1999)

McMillan, K.L.: Cadence SMV. Available from, http://embedded.eecs.berkeley.edu/Alumni/kenmcmil/smv/

Meng, S., Naixiao, Z., Barbosa, L.S.: On Semantics and Refinement of UML Statecharts: A Coalgebraic View. SEFM ’04: Proceedings of the Software Engineering and Formal Methods, Second International Conference on (SEFM’04), 00:164–173 (2004)

Mikk, E., Lakhnech, Y., Siegel, M., Holzmann, G.J.: Implementing Statecharts in Promela/SPIN. In: Proceedings of the 2nd IEEE Workshop on Industrial-Strength Formal Specification Techniques, October 1998, pp. 90–101. IEEE Computer Society Press, Los Alamitos (1998)

Paltor, I., Lilius, J.: Formalising UML State Machines for Model Checking. In: UML, pp. 430–445 (1999)

Paltor, I.P., Lilius, J.: vUML: A Tool for Verifying UML Models. In: Hall, R.J., Tyugu, E. (eds.) Proc. of the 14th IEEE International Conference on Automated Software Engineering, ASE’99, IEEE Computer Society Press, Los Alamitos (1999)

Ramalingam, G.: Context-Sensitive Synchronization-Sensitive Analysis is Undecidable. ACM Trans. Program. Lang. Syst. 22(2), 416–430 (2000), doi:10.1145/349214.349241

Wang, J., Dong, W., Qi, Z.-C.: Slicing Hierarchical Automata for Model Checking UML Statecharts. In: George, C.W., Miao, H. (eds.) ICFEM 2002. LNCS, vol. 2495, pp. 435–446. Springer, Heidelberg (2002)

Author information

Authors and Affiliations

Editor information

Rights and permissions

Copyright information

© 2007 Springer Berlin Heidelberg

About this paper

Cite this paper

Van Langenhove, S., Hoogewijs, A. (2007). SVtL: System Verification Through Logic Tool Support for Verifying Sliced Hierarchical Statecharts. In: Fiadeiro, J.L., Schobbens, PY. (eds) Recent Trends in Algebraic Development Techniques. WADT 2006. Lecture Notes in Computer Science, vol 4409. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-540-71998-4_9

Download citation

DOI: https://doi.org/10.1007/978-3-540-71998-4_9

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-71997-7

Online ISBN: 978-3-540-71998-4

eBook Packages: Computer ScienceComputer Science (R0)