Abstract

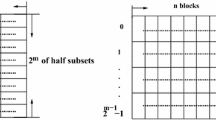

In this paper, a multi-way way prediction policy (MWWP) with a two-port Way Predictor (TPWP) is proposed for reducing the dynamic and leakage energy in multi-way set associative drowsy I-Cache without dramatic loss of performance. One port of TPWP is used for predicting the matching way in current set, only the predicted way and not all the ways is accessed to reduce the dynamic energy. The other is used for predicting the matching way in subsequent set, only the cache line in predicted way is pre-woken up from the drowsy mode to reduce the leakage energy. Different with the traditional way prediction policy, the MWWP has the lower performance overhead by selecting multiple ways speculatively for each access to improve way prediction hit ratio (WPHR). The simulation and estimation results show that, in a 4-way set-associative drowsy I-Cache, with 0.98% and 0.4% performance overhead respectively, our proposed 2-way and 3-way way prediction policy with TPWP can reduce 59% and 47% of energy in I-Cache, and save the 6.1% and 5.4% of the whole processor energy. The EDP is improved by 4.5% and 4.1% on average.

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Gowan, M.K., Biro, L.L., Jackson, D.B.: Power Considerations in the Design of the Alpha 21264 Microprocessor. In: DAC’98, Los Alamitos, California, U.S., pp. 26–31 (1998)

Manne, S., Klauser, A., Grunwald, D.: Pipeline Gating: Speculation Control for Energy Reduction. In: Proc. Of Int. Symp. on Computer Architecture, pp. 132–141 (1998)

Powell, M.D., et al.: Gated-Vdd: A Circuit Technique to Reduce Leakage in Deep- Submicron Cache Memories. In: ISLPED2000, pp. 90–95 (2000)

Kaxiras, S., Hu, Z., Martonosi, M.: Cache Decay: Exploiting Generational Behavior to Reduce Cache Leakage Power. In: ISCA2001, pp. 240–251 (2001)

Kim, N.S., Flautner, K., Blaauw, D., Mudge, T.: Circuit and Microarchitectural Techniques for Reducing CacheLeakage Power. IEEE Transaction on VLSI Systems 12(2), 167–184 (2004)

Zhang, Y., Parikh, D., Sankaranarayanan, K., Skadron, K., Stan, M.R.: Hotleakage: An Architectural, Temperature-aware Model of Subthreshold and Gate Leakage. Tech. Report CS-2003-05, Department of Computer Sciences, University of Virginia (2003)

Zhang, C., Zhou, H., Zhang, M.X., Xing, Z.: An architectural leakage power reduction method for instruction cache in ultra deep submicron microprocessors. In: Jesshope, C., Egan, C. (eds.) ACSAC 2006. LNCS, vol. 4186, pp. 588–594. Springer, Heidelberg (2006)

Chung, S.W., Skadron, K.: Using Branch Prediction Information for Near-Optimal I-Cache Leakage. In: Jesshope, C., Egan, C. (eds.) ACSAC 2006. LNCS, vol. 4186, pp. 24–37. Springer, Heidelberg (2006)

Inoue, K., Ishihara, T., Murakami, K.: Way-predicting Set-Associative Cache for High performance and Low Energy Consumption. In: Proc. Of 1999 International Symposium on low power Electronics and Design (ISLPED1999), pp. 273–275 (1999)

Flautner, K., Kim, N.S., Martin, S., Blaauw, D., Mudge, T.: Drowsy Caches: Simple Techniques for Reducing Leakage Power. In: ISCA2002, pp. 147–157 (2002)

SIA: International Technology Roadmap for Semiconductors (2004)

Segars, S.: Low Power Design Techniques for Microprocessors. ISSCC Tutorial (2001)

Author information

Authors and Affiliations

Editor information

Rights and permissions

Copyright information

© 2007 Springer Berlin Heidelberg

About this paper

Cite this paper

Hongwei, Z., Chengyi, Z., Mingxuan, Z. (2007). Improved Way Prediction Policy for Low-Energy Instruction Caches. In: Lee, YH., Kim, HN., Kim, J., Park, Y., Yang, L.T., Kim, S.W. (eds) Embedded Software and Systems. ICESS 2007. Lecture Notes in Computer Science, vol 4523. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-540-72685-2_40

Download citation

DOI: https://doi.org/10.1007/978-3-540-72685-2_40

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-72684-5

Online ISBN: 978-3-540-72685-2

eBook Packages: Computer ScienceComputer Science (R0)