Abstract

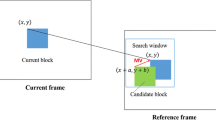

This paper presents a parallel architecture that can simultaneously perform block-matching motion estimation (ME) and discrete cosine transform (DCT). Because DCT and ME are both processed block by block, it is preferable to put them in one module for resource sharing. Simulation results performed using Simulink demonstrate that the parallel fashioned architecture improves the performance in terms of running time by 18.6% compared to the conventional sequential fashioned architecture.

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Haskell, B.: An introduction to MPEG-2. Chapman & Hall, Sydney (1996)

Ahemd, N., Natarajan, T., Rao, K.R.: Discrete cosine transform. IEEE Trans. Computers C-23, 90–93 (1974)

Guttag, K., Gove, R.J., Van Aken, J.R.: A single chip multiprocessor for multimedia: The mvp. IEEE Computer Graphics and Applications, pp. 53–64 (1992)

Shengqi, Y., Wayne, W., Vijaykrishnan, N.: Power and Performance Analysis of Motion Estimation Based on Hardware and Software Realizations. IEEE Transactions on Computers 54, 714–726 (2005)

Li, R., Zeng, B., Liou, M.L.: A New Three-Step Search Algorithm for Block Motion Estimation. IEEE Transactions on Circuit and System for Video Technology 4, 438–442 (1994)

Po, L.M., Ma, W.C.: A Novel Four-Step Search Algorithm for Fast Block Motion Estimation. IEEE Transactions on Circuit and System for Video Technology 6, 313–317 (1996)

Liu, B., Zaccarin, A.: New Fast Algorithms for the Estimation of Block Motion Vectors. IEEE Transactions on Circuit and System for Video Technology 3, 148–157 (1993)

Chen, W., Smith, C.H., Fralick, S.: A fast computation algorithm for the discrete cosine transform. IEEE Transactions on communications 25, 1004–1009 (1977)

Lee, Y.P., et al.: A cost effective architecture for 8*8 two-dimensional DCT/IDCT using direct method. IEEE Transactions on Circuit and system for video technology 7, 459–467 (1997)

Loeffler, C., Lightenberg, A., Moschytz, G.S.: Practical fast 1-D DCT algorithm with 11 multiplications. In: Proceedings of ICASSP, vol. 2, pp. 988–991 (1989)

Kung, S.Y.: VLSI Array Processors. Prentice-Hall, Englewood Cliffs (1998)

Nam, S.H., Baek, J.S., Lee, M.K.: Flexible VLSI architecture of full search motion estimation for video applications. IEEE Transactions on Consumer Electronics 40, 176–184 (1994)

Eric, C., Sethuraman, P.: Motion Estimation Architecture for Video Compression. IEEE Transactions on Consumer Electronics 39, 292–297 (1993)

Jiang, M., Luo, Y., Fu, Y.L., Yang, B., Zhao, B.Y.: A low power 1D-DCT Processor for MPEG-targeted Real-time Applications. International Symposium on Communications and Information Technologies, pp. 682–687 (2004)

Nam, J., Choi, T.S.: A Fast Full-Search Motion-Estimation Algorithm Using Representative Pixels and Adaptive Matching Scan. IEEE Transactions on Circuits and Systems for Video Technology 10, 1040–1048 (2000)

Author information

Authors and Affiliations

Editor information

Rights and permissions

Copyright information

© 2007 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Huang, J., Li, H. (2007). A Parallel Architecture for Motion Estimation and DCT Computation in MPEG-2 Encoder. In: Jin, H., Rana, O.F., Pan, Y., Prasanna, V.K. (eds) Algorithms and Architectures for Parallel Processing. ICA3PP 2007. Lecture Notes in Computer Science, vol 4494. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-540-72905-1_19

Download citation

DOI: https://doi.org/10.1007/978-3-540-72905-1_19

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-72904-4

Online ISBN: 978-3-540-72905-1

eBook Packages: Computer ScienceComputer Science (R0)