Abstract

Impulse Radio-based Ultra-Wideband (UWB) technology is a strong candidate for the implementation of ultra low power air interfaces in low data rate sensor networks. A major challenge in UWB receiver design is the low-power implementation of the relatively complex digital baseband algorithms that are required for timing acquisition and data demodulation. Silicon Hive offers low-power application specific instruction set processor (ASIP) solutions. In this paper we target the low-power implementation of an UWB receiver’s digital baseband algorithm on an ASIP, based on Silicon Hive’s solutions.

We approach the problem as follows. First we implement the algorithm on an existing ASIP and analyze the power consumption. Next we apply optimizations such as algorithmic simplification, adding a loopcache and adding custom operations to lower the dissipation of the ASIP. The resulting ASIP consumes 0.98 nJ (with a spreading factor of 16) per actual data bit, which is lower than an existing application specific integrated circuit (ASIC).

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

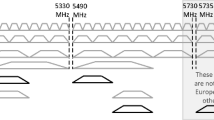

IEEE Std P802.15.4a/d6, PART 15.4: wireless medium access control (MAC) and physical layer (PHY) specifications for low-rate wireless personal area networks (LR-WPANs): amendment to add alternate PHY (2006)

Badaroglu, M., Desset, C., Ryckaert, J., et al.: Analog-digital partitioning for low-power UWB impulse radios under CMOS scaling. EURASIP Journal on Wireless Communications and Networking 2006, Article ID 72430 8 (2006)

Ryckaert, J., Badaroglu, M., Desset, C., et al.: Carrier-based UWB impulse radio: simplicity, flexibility, and pulser implementation in 180 nm CMOS. In: CU 2005. Proceedings of the IEEE International Conference on Ultra-Wideband, Zurich, Switzerland, pp. 432–437 (2005)

Ryckaert, J., Badaroglu, M., DeHeyn, V., et al.: A 16mA UWB 3-to-5GHz 20MPulses/s quadrature analog correlation receiver in 180 nm CMOS. In: Proceedings of IEEE International Solid-State Circuits Conference, Digest of Technical Papers, San Francisco Marriott, California, USA (2006)

Kastrup, B., van Wel, A.: Moustique: Smaller than an ASIC and fully programmable. In: International Symposium on System-on-Chip 2003, Silicon Hive, Philips Technology Incubator, The Netherlands, vol. 2003 (2003)

Patterson, D.A., Hennessy, J.L.: Computer organization and design, 2nd edn. The hardware/software interface. Morgan Kaufmann Publishers Inc, San Francisco (1998)

Munch, M., Wurth, B., Mehra, R., Sproch, J., Wehn, N.: Automating RT-level operand isolation to minimize power consumption in datapaths. In: DATE 2000. Proceedings of the conference on Design, automation and test in Europe, pp. 624–633. ACM Press, New York (2000)

Li, H., Bhunia, S., Chen, Y., Vijaykumar, T.N., Roy, K.: Deterministic clock gating for microprocessor power reduction. In: HPCA 2003. Proceedings of the 9th International Symposium on High-Performance Computer Architecture, p. 113. IEEE Computer Society Press, Washington, DC, USA (2003)

Garrett, D., Stan, M., Dean, A.: Challenges in clockgating for a low power ASIC methodology. In: ISLPED 1999. Proceedings of the 1999 international symposium on Low power electronics and design, pp. 176–181. ACM Press, New York (1999)

Heo, S.: A low-power 32-bit datapath design. Master’s thesis, Massachusetts Institute of Technology (2000)

Jiang, H., Marek-Sadowska, M., Nassif, S.R.: Benefits and costs of power-gating technique. In: ICCD 2005. Proceedings of the 2005 International Conference on Computer Design, pp. 559–566. IEEE Computer Society, Washington, DC, USA (2005)

Agarwal, K., Deogun, H.S., Sylvester, D., Nowka, K.: Power gating with multiple sleep modes. In: ACM/IEEE International Symposium on Quality Electronic Design (2006)

Arnold, M., Corporaal, H.: Automatic detection of recurring operation patterns. In: CODES 1999, pp. 22–26. ACM Press, New York (1999)

Athanas, P.M., Silverman, H.F.: Processor reconfiguration through instruction-set metamorphosis. Computer 26(3), 11–18 (1993)

Ysebodt, L., Nil, M.D., Huisken, J., Berekovic, M., Zhao, Q., Bouwens, F.J., van Meerbergen, J.: Design of low power wireless sensor nodes on energy scanvengers for biomedical monitoring. In: Vassiliadis, S., Bereković, M., Hämäläinen, T.D. (eds.) SAMOS 2007. LNCS, vol. 4599, Springer, Heidelberg (2007)

Author information

Authors and Affiliations

Editor information

Rights and permissions

Copyright information

© 2008 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Govers, J. et al. (2008). Implementation of an UWB Impulse-Radio Acquisition and Despreading Algorithm on a Low Power ASIP. In: Stenström, P., Dubois, M., Katevenis, M., Gupta, R., Ungerer, T. (eds) High Performance Embedded Architectures and Compilers. HiPEAC 2008. Lecture Notes in Computer Science, vol 4917. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-540-77560-7_7

Download citation

DOI: https://doi.org/10.1007/978-3-540-77560-7_7

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-77559-1

Online ISBN: 978-3-540-77560-7

eBook Packages: Computer ScienceComputer Science (R0)