Abstract

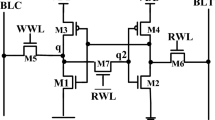

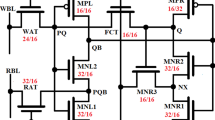

This paper proposes a low power SRAM based on five transistor SRAM cell. Proposed SRAM uses novel word-line decoding such that, during a read/write operation, only selected cell is connected to bit-line when one row is selected whereas, in conventional SRAM (CV-SRAM), all cells in selected row connected to their bit-lines, which in turn develops differential voltages across all bit-lines, and this makes energy consumption on unselected bit-lines. Proposed SRAM uses one bit-line and thus has lower bit-line leakage compared to CV-SRAM. Furthermore, the proposed SRAM incurs no area overhead, and has comparable read/write performance versus the CV-SRAM. Simulation results in standard 0.25μm CMOS technology shows in worst case proposed SRAM has on average 80% smaller energy consumption in each cycle compared to CV-SRAM. Besides, energy consumption in each cycle of proposed SRAM and CV-SRAM investigated analytically, the results of which are in good agreement with the simulation results.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Amelifard, B., Fallah, F., Pedram, M.C.: Low-leakage SRAM design with dual Vt transistors. In: 7th IEEE International Symposium on Quality of Electronic Designs. IEEE Press, Los Alamitos (2006)

Martin, K., C.: Digital Integrated Circuit Design. Oxford university press, New York (2000)

Hirose, T., Kuriyama, H., Mnmkami, S., Yuzuriha, K., Mukai, T., et al.: A 20-ns 4-Mb CMOS SRAM with Hierarchical Word Decoding Architecture. IEEE Journal of Solid-State Circuits 25, 1068–1074 (1990)

Carlson, I., Andersson, S., Natarajan, S., Alvandpour, A.C.: A high density, low leakage, 5T SRAM for embedded caches. In: Proc. of European Solid-State Circuits Conference, pp. 215–222. IEEE Press, Los Alamitos (2004)

Rabaey, J.M., et al.: Digital Integrated Circuits: A Design Perspective. Prentice Hall, Englewood Cliffs (2002)

Azizi Mazreah, A., Manzuri Shalmani, M.T., Barati, H., Barati, A.C.: Delay and Energy Consumption Analysis of Conventional SRAM. International Journal of Electronics, Circuits and System 2(2), 35–39 (2008)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2008 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Azizi Mazreah, A., Manzuri Shalmani, M.T. (2008). A Low Power SRAM Based on Five Transistors Cell. In: Sarbazi-Azad, H., Parhami, B., Miremadi, SG., Hessabi, S. (eds) Advances in Computer Science and Engineering. CSICC 2008. Communications in Computer and Information Science, vol 6. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-540-89985-3_83

Download citation

DOI: https://doi.org/10.1007/978-3-540-89985-3_83

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-89984-6

Online ISBN: 978-3-540-89985-3

eBook Packages: Computer ScienceComputer Science (R0)