Abstract

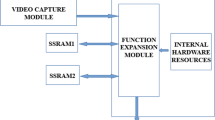

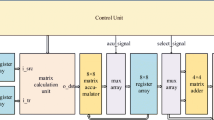

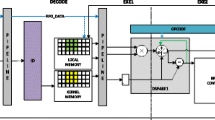

This paper presents a general-purpose, multi-task, and reconfigurable platform for video and image processing. With the increasing requirements of processing power in many of today’s video and image processing applications, it is important to go beyond the software implementation to provide a real-time, low cost, high performance, and scalable hardware platform. In this paper, we propose a system by using the powerful parallel processing architecture in the Field Programmable Gate Array (FPGA) to achieve this objective. Based on the proposed system level architecture and design strategies, a prototype system is developed based on the Xilinx Virtex-II FPGA with the integration of embedded processor, memory control and interface technologies. Our system includes different functional modules, such as edge detection, zoom-in and zoom-out functions, which provides the flexibility of using this system as a general video processing platform according to different application requirements. The final system utilizes about 20% of logic resource, 50% of memory on chip, and has total power consumption around 203 mw.

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Video and Image Processing Design Using FPGAs, Altera Corporation, http://www.altera.com/literature/wp/wp-video0306.pdf

Benkrid, K., Crookes, D., Benkrid, A.: Towards a General Framework for FPGA Based Image Processing Using Hardware Skeletons. Parallel Computing 28(7-8), 1141–1154 (2002)

Johnston, C.T., Gribbon, K.T., Bailey, D.G.: Implementing Image Processing Algorithms on FPGAs. In: Proc. Electronics New Zealand Conference, Palmerston North, New Zealand, pp. 118–123 (2004)

Kim, C.H., Seong, S.M., Lee, J.A., Kim, L.S.: An Image-Scaling Algorithm Using an Area Pixel Model. IEEE Trans. Circuits and Systems for Video Technology 13(6), 549–553 (2003)

Fry, T.W., Hauck, S.A.: SPIHT Image Compression on FPGAs. IEEE Trans. Circuits and Systems for Video Technology 15(9), 1138–1147 (2005)

Daz, J., Ros, E., Pelayo, F., Ortigosa, E.M., Mota, S.: FPGA-Based Real-Time Optical-Flow System. IEEE Trans. Circuits and Systems for Video Technology 16(2), 274–279 (2006)

Ku, C.C., Liang, R.K.: Accurate Motion Detection and Sawtooth Artifacts Remove Video Processing Engine for LCD TV. IEEE Trans. Consumer Electronics 50(4), 1194–1201 (2004)

Leelarasmee, E.: A TV Sign Image Expander with Built-in Closed Caption Decoder. IEEE Trans. Consumer Electronics 51(2), 682–687 (2005)

Zhang, H., Xia, M., Hu, G.: A Multiwindow Partial Buffering Scheme for FPGA-Based 2-D Convolvers. IEEE Trans. Circuits and Systems, Part II 54(2), 200–204 (2007)

Fel, S., Fttinger, G., Mohr, J.: Motion JPEG2000 for High Quality Video Systems. IEEE Trans. Consumer Electronics 49(4), 787–791 (2003)

Madanayake, A., Bruton, L.: A Fully Multiplexed First-Order Frequency-Planar Module for Fan, Beam, and Cone Plane-Wave Filters. IEEE Trans. Circuits and Systems, Part II 53(8), 697–701 (2006)

Virtex-II Pro family (XC2VP30), Data sheet, http://www.xilinx.com/products/silicon_solutions/fpgas/virtex/virtex_ii_pro_fpgas/index.htm

Dhawan, A.P.: Medical Image Analysis, pp. 175–210. Wiley-interscience Press, Hoboken (2003)

Jahne, B.: Digital Image Processing, 5th edn., pp. 427–440. Springer, Berlin (2002)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2009 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Li, J., He, H., Man, H., Desai, S. (2009). A General-Purpose FPGA-Based Reconfigurable Platform for Video and Image Processing. In: Yu, W., He, H., Zhang, N. (eds) Advances in Neural Networks – ISNN 2009. ISNN 2009. Lecture Notes in Computer Science, vol 5553. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-01513-7_32

Download citation

DOI: https://doi.org/10.1007/978-3-642-01513-7_32

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-01512-0

Online ISBN: 978-3-642-01513-7

eBook Packages: Computer ScienceComputer Science (R0)