Abstract

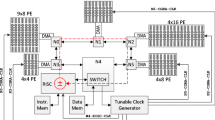

With the emergence of high-performance multi-core microprocessors in the sub-45nm technology era, specialized hardware accelerator engines embedded within the core architecture have the potential to achieve 10-100X increase in energy efficiency across a wide domain of compute-intensive signal processing and scientific algorithms. In this talk, we present multi-core microprocessors integrated with on-die energy-efficient reconfigurable accelerator and co-processor engines to achieve well beyond tera-scale performance in sub-45nm technologies. Recent trends and advances in multi-core microprocessors will be presented, followed by key enablers for reconfigurability of specialized hardware engines to support multiple protocols while substantially improving time-to-market and amortizing die area cost across a wide range of compute workloads and functions. Specific design examples and case studies supported by silicon measurements will be presented to demonstrate reconfigurable engines for wireless baseband, signal processing and graphics/media applications. Power efficient optimization of reconfigurable processors to support fine-grain power management, dynamic on-the-fly configurability and standby-mode leakage reduction and low-voltage operability will also be described.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2010 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Krishnamurthy, R. (2010). High-Performance Energy-Efficient Reconfigurable Accelerators/Co-processors for Tera-Scale Multi-core Microprocessors. In: Sirisuk, P., Morgan, F., El-Ghazawi, T., Amano, H. (eds) Reconfigurable Computing: Architectures, Tools and Applications. ARC 2010. Lecture Notes in Computer Science, vol 5992. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-12133-3_1

Download citation

DOI: https://doi.org/10.1007/978-3-642-12133-3_1

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-12132-6

Online ISBN: 978-3-642-12133-3

eBook Packages: Computer ScienceComputer Science (R0)