Abstract

This paper presents a design flow for secure software (SW) implementations of cryptographic algorithms against Side-Channel Attacks (SCAs) by using a CPU modification. The development of countermeasures to increase resistance against the SCAs in SW implementations is a topic of ongoing research. Researchers have proposed SW-level countermeasures in order to defeat the SCAs. However, we notice that more secure SW implementations are possible with an additional support from a hardware (HW) level countermeasure such as partial CPU modifications. This paper proposes a co-design approach of SW-level countermeasures and CPU modifications to defeat the SCAs on Field Programmable Gate Arrays (FPGA). As a case study of evaluating an effectiveness of the combination of our SW-/HW-level countermeasures, the S-box algorithm proposed by Coron et al. [1] is used. According to our experimental results, we find that the algorithm can be performed with a higher resistance against power analysis by applying our countermeasures. Our proposed design flow is applicable to various kinds of algorithms as well.

This research was partially supported by Strategic International Cooperative Program (Joint Research Type), Japan Science and Technology Agency.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Coron, J.-S., Giraud, C., Prouff, E., Rivain, M.: Attack and Improvement of a Secure S-Box Calculation Based on the Fourier Transform. In: Oswald, E., Rohatgi, P. (eds.) CHES 2008. LNCS, vol. 5154, pp. 1–14. Springer, Heidelberg (2008)

National Institute of Standards and Technology (NIST), FIPS PUB 197: the official AES standard, http://www.csrc.nist.gov/publications/fips/fips197/fips-197.pdf

Tiri, K., Verbauwhede, I.: A Logic Level Design Methodology for a Secure DPA Resistant ASIC or FPGA Implementation. In: Proceedings of the Conference on Design, Automation and Test in Europe, DATE 2004, pp. 246–251. IEEE Computer Society, Los Alamitos (2004)

Suzuki, D., Saeki, M., Ichikawa, T.: Random Switching Logic: A Countermeasure against DPA Based on Transition Probability. Cryptology ePrint Archive (2004)

Batina, L., Hwang, D., Hodjat, A., Preneel, B., Verbauwhede, I.: Hardware/Software Co-design for Hyperelliptic Curve Cryptography (HECC) on the 8051μP. In: Rao, J.R., Sunar, B. (eds.) CHES 2005. LNCS, vol. 3659, pp. 106–118. Springer, Heidelberg (2005)

Sakiyama, K., Batina, L., Preneel, B., Verbauwhede, I.: Superscalar Coprocessor for High-Speed Curve-Based Cryptography. In: Goubin, L., Matsui, M. (eds.) CHES 2006. LNCS, vol. 4249, pp. 415–429. Springer, Heidelberg (2006)

Kocher, P., Jaffe, J., Jun, B.: Differential Power Analysis. In: Wiener, M. (ed.) CRYPTO 1999. LNCS, vol. 1666, pp. 388–397. Springer, Heidelberg (1999)

Kocher, P.: Timing Attacks on Implementations of Diffie-Hellman, RSA, DSS, and Other Systems. In: Koblitz, N. (ed.) CRYPTO 1996. LNCS, vol. 1109, pp. 104–113. Springer, Heidelberg (1996)

Messerges, T.S.: Using Second-Order Power Analysis to Attack DPA Resistant Software. In: Paar, C., Koç, Ç.K. (eds.) CHES 2000. LNCS, vol. 1965, pp. 238–251. Springer, Heidelberg (2000)

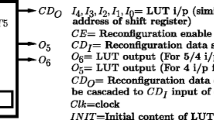

XILINX, PicoBlaze 8-bit Embedded Microcontroller User Guide, http://www.xilinx.com/support/documentation/ip_documentation/ug129.pdf

Itoh, K., Izu, T., Takenaka, M.: A Practical Countermeasure against Address-Bit Differential Power Analysis. In: Walter, C.D., Koç, Ç.K., Paar, C. (eds.) CHES 2003. LNCS, vol. 2779, pp. 382–396. Springer, Heidelberg (2003)

Coron, J.-S., Goubin, L.: On Boolean and Arithmetic Masking against Differential Power Analysis. In: Paar, C., Koç, Ç.K. (eds.) CHES 2000. LNCS, vol. 1965, pp. 231–237. Springer, Heidelberg (2000)

Goubin, L.: A Sound Method for Switching between Boolean and Arithmetic Masking. In: Koç, Ç.K., Naccache, D., Paar, C. (eds.) CHES 2001. LNCS, vol. 2162, pp. 3–15. Springer, Heidelberg (2001)

Li, Y., Sakiyama, K., Kawamura, S., Komano, Y., Ohta, K.: Security Evaluation of a DPA-Resistant S-box Based on the Fourier Transform. In: International Conference on Information and Communications Security. LNCS, vol. 5927, pp. 3–16. Springer, Heidelberg (2009)

Suzuki, D., Saeki, M., Ichikawa, T.: Random Switching Logic: A New Countermeasure against DPA and Second-Order DPA at the Logic Level. IEICE Trans. Fundamentals E90-A(1), 160–168 (2007)

National Institute of Advanced Industrial Science and Technology (AIST), Side-channel Attack Standard Evaluation Board (SASEBO), http://www.rcis.aist.go.jp/special/SASEBO/index-en.html

Clavier, C., Coron, J.-S., Dabbous, N.: Differential Power Analysis in the Presence of Hardware Countermeasures. In: Paar, C., Koç, Ç.K. (eds.) CHES 2000. LNCS, vol. 1965, pp. 252–263. Springer, Heidelberg (2000)

Dichtl, M., Golić, J.D.: High-Speed True Random Number Generation with Logic Gates Only. In: Paillier, P., Verbauwhede, I. (eds.) CHES 2007. LNCS, vol. 4727, pp. 45–62. Springer, Heidelberg (2007)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2011 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Nakatsu, D., Li, Y., Sakiyama, K., Ohta, K. (2011). Combination of SW Countermeasure and CPU Modification on FPGA against Power Analysis. In: Chung, Y., Yung, M. (eds) Information Security Applications. WISA 2010. Lecture Notes in Computer Science, vol 6513. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-17955-6_19

Download citation

DOI: https://doi.org/10.1007/978-3-642-17955-6_19

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-17954-9

Online ISBN: 978-3-642-17955-6

eBook Packages: Computer ScienceComputer Science (R0)