Abstract

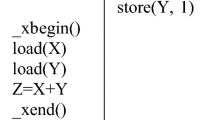

In Transactional Memory (TM) for multicore systems, contention management refers to the mechanisms used to guarantee forward to avoid performance pathologies, and to promote throughput. The choice of contention management police impacts strongly on the performance of applications. In this paper, we study contention management policies for Hardware Transactional Memory (HTM). Although the results were obtained from a HTM framework, the conclusions and proposals are applicable to any type of TM: hardware, software or hybrid. We first characterize transactions’ behaviors on execution time.We find that significant time is wasted when few transactions forward progress due to the data conflicts among different transactions. To reduce this kind of waste time, we propose a novel contention management(CM) scheme that reduces waste time and guarantees forwarding. We evaluate our techniques using a detailed execution-driven simulator. The results show that our scheme can effectively minimize the amount of waste time and, consequently, decrease execution time than previous approaches for large transactions.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Herlihy, M., Moss, J.E.B.: Transactional Memory: architectural support for Lock- Free data structures. In: Proceedings of the 20th Annual International Symposium on Computer Architecture. Conference Proceedings - Annual Symposium on Computer Architecture, San Diego, CA, USA, pp. 289–300. IEEE Press, Los Alamitos (1993)

Larus, J.R., Rajwar, R.: Transactional Memory. Morgan & Claypool Publishers, San Rafael (2006)

Damron, P., Fedorova, A., Lev, Y., Luchangco, V., Moir, M., Nussbaum, D.: Hybrid transactional memory. In: Proceedings of the 12th International Conference on Architectural Support for Programming Languages and Operating Systems, ASPLOS-XII, pp. 336–346. ACM, New York (2006)

Scherer III, W.N., Scott, M.L.: Randomization in STM Contention Management (POSTER). In: Proceedings of the 24th ACM Symposium on Principles of Distributed Computing, Las Vegas, NV (2005)

Bobba, J., Moore, K.E., Volos, H., Yen, L., Hill, M.D., Swift, M.M., Wood, D.A.: Performance pathologies in hardware transactional memory. In: Proceedings of the International Symposium on Computer Architecture, San Diego, CA, USA, pp. 81–91. IEEE Press, Los Alamitos (2007)

Ramadan, H.E., Rossbach, C.J., Witchel, E.: Dependence-aware transactional memory for increased concurrency. In: Proceedings of the 2008 41st IEEE/ACM International Symposium on Microarchitecture, MICRO 2008, pp. 246–257. IEEE Computer Society Press, Los Alamitos (2008)

Yen, L.: Signatures in Transactional Memory systems. PhD thesis, Department of Computer Science, University of Wisconsin-Madison, WI, USA (2009)

Martin, M.M.K., Sorin, D.J., Beckmann, B.M., Marty, M.R., Xu, M., Alameldeen, A.R., Moore, K.E., Hill, M.D., Wood, D.A.: Multifacet’s general execution-driven multiprocessor simulator (GEMS) toolset. SIGARCH Comput. Archit. News 33, 92–99 (2005)

Magnusson, P.S., Christensson, M., Eskilson, J., Forsgren, D., Hallberg, G., Hogberg, J., Larsson, F., Moestedt, A., Werner, B.: Simics: A full system simulation platform. Computer 35, 50–58 (2002)

Yen, L., Bobba, J., Marty, M.R., Moore, K.E., Volos, H., Hill, M.D., Swift, M.M., Wood, D.A.: LogTM-SE: decoupling Hardware Transactional Memory from caches. In: Proceedings of the IEEE 13th International Symposium on High Performance Computer Architecture, Scottsdale, AZ, USA, pp. 261–272. IEEE Press, Los Alamitos (2007)

Herlihy, M., Luchangco, V., Moir, M., Scherer III, W.N.: Software Transactional Memory for Dynamic-Sized data structures. In: Proceedings of the 22nd Annual Symposium on Principles of Distributed Computing, Boston, Massachusetts, USA, pp. 92–101. ACM Press, New York (2003)

Woo, S.C., Ohara, M., Torrie, E., Singh, J.P., Gupta, A.: The SPLASH-2 programs: characterization and methodological considerations. In: Proceedings of the 22nd Annual International Symposium on Computer Architecture, ISCA 1995, pp. 24–36. ACM, New York (1995)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2011 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Fu, C., Wen, D., Wang, X., Yang, X. (2011). An Effective Conflict Management for Large Transactions in Hardware Transactional Memory System. In: Qi, L. (eds) Information and Automation. ISIA 2010. Communications in Computer and Information Science, vol 86. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-19853-3_57

Download citation

DOI: https://doi.org/10.1007/978-3-642-19853-3_57

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-19852-6

Online ISBN: 978-3-642-19853-3

eBook Packages: Computer ScienceComputer Science (R0)