Abstract

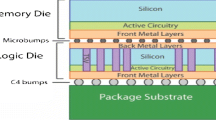

In the embedded system design Through-silicon-via (TSV) based 3D stacked ICs (SICs) play an important role in semiconductor industry. But testing of these SICs are required during 3D assembly because different die stacking steps may introduce defects. In this paper, we address test architecture optimization for 3D stacked ICs implemented with hard die means where die-level test architecture is fixed. We consider two different SIC configurations and derive optimal solution to minimize overall test time when complete stack and multiple partial stacks, need to be tested. Results are performed for two handcrafted 3D SICs comprising of various SoCs from ITC’02 SoC test benchmarks. In this work we consider the test architecture optimization for 3D SIC where each die consists of one SoC. We present test schedules and corresponding test lengths for every multiple insertions and also show that total test lengths are decreased with the increasing number of test pins.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Iyengar, K.C., Marinissen, E.J.: Test Wrapper and Test Access Mechanism Co-optimization for System-on-chip. International Journal of Electronic Testing, Theory and Appilicatios 18, 213–230 (2002)

Wu, X., Chen, Y., Chakrabarty, K., Xie, Y.: Test-access mechanism optimization for core-based three-dimensional SOCs. In: IEEE International Conference on Computer Design, pp. 212–218 (2008)

Lee, H.S., Chakrabarty, K.: Test Challenges for 3DIntegrated Circuits. IEEE Design and Test of Computers 26, 26–35 (2009)

Noia, B., Goel, S.K., Chakrabarty, K., Marinissen, E.J., Verbree, J.: Test Architecture Optimization for TSV-Based 3D Stacked ICs. In: IEEE Intl. Conf. on European Test Symposium, pp. 24–29 (2009)

Marinissen, E.J., Verbree, J., Konijnenburg, M.: A Structured and Scalable Test Access Architecture for TSV-Based 3D Stacked ICs. In: IEEE Intl. Conf. VLSI Test Symposium, pp. 269–274 (2010)

Noia, B., Chakrabarty, K., Marinissen, E.J.: Optimization Methods for Post-Bond Die-Internal/External Testing in 3D stacked ICs. In: IEEE Intl. Conf. Test Conference (ITC), pp. 1–9 (2010)

Noia, B., Chakraborty, K., Goel, S.K., Marinissen, E.J., Verbree, J.: Test-Architecture Optimization and Test Scheduling for TSV-Based 3-D Stacked ICs. IEEE Transaction on Computer Aided Design of Integrated Circuit and System 30, 1705–1718 (2011)

Bushnell, M.L., Agarawal, V.D.: Essentials of electronic testing. Springer Publishers

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2012 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Roy, S.K., Roy, D., Giri, C., Rahaman, H. (2012). Post-bond Stack Testing for 3D Stacked IC. In: Rahaman, H., Chattopadhyay, S., Chattopadhyay, S. (eds) Progress in VLSI Design and Test. Lecture Notes in Computer Science, vol 7373. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-31494-0_8

Download citation

DOI: https://doi.org/10.1007/978-3-642-31494-0_8

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-31493-3

Online ISBN: 978-3-642-31494-0

eBook Packages: Computer ScienceComputer Science (R0)