Abstract

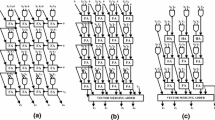

Reconfigurable architecture using FPGA devices provide a method to utilize the available logic resources on the chip for various computations. The basic ability of reconfigurable computing is to perform computations in hardware to increase performance, while retaining the flexibility of application software. The purpose of this paper is to evaluation of computational delay of FPGA devices for reconfigurable computing system by mixing of Look up tables (LUTs) and Programmable logic arrays (PLAs) architecture. The two main types of programmable logic devices, field-programmable gate arrays (FPGA) based on LUTs technology and complex programmable logic device (CPLD) based on PLAs technology. They are both widely used and each contributing particular strengths in the area of reconfigurable system design. We identified Hybrid LUTs/PLAs architectures as Hybrid Reconfigurable Computing Architectures (HRCA). The basis of the HRCA is that some parts of digital circuits are well-suited for execution with LUTs, but other parts help more from the PLAs structures. For several classes of high performance applications, HRCA offers significant savings in total computational delay comparison with a symmetrical FPGA which contain only LUTs. It also offers some improvements in logical area and power consumption.Experimental results based on MCNC benchmark circuit were performed on implemented CAD and compare between HRCA and symmetrical FPGA. Initially results indicate that noteworthy computational delay of symmetrical FPGA is reduced by using HRCA.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Kaviani, A., Brown, S.: The Hybrid Field Programmable Architecture. IEEE Design & Test of Computer, 74–83 (1999)

Zeidman, B.: Designing with FPGAs and CPLDs. CMP Books, Canada (2002)

Bobda, C.: Introduction to Reconfigurable Computing Architectures, Algorithms, and Applications. University of Kaiserslautern, Germany (2007)

Hauck, S., DeHon, A.: Reconfigurable Computing: The theory and Practice of FPGA. Elsevier Book (2008)

Cong, J., Ding, Y.: Survey Paper - Combinational Logic Synthesis for LUT based Field Programmable Gate Arrays. ACM DAES 1(2), 145–204 (1996)

The Altera Stratix Device Handbook (2005), http://www.altera.com

Rose, J., et al.: Architecture of FPGA: The Effect of Logic Block Functionality on Area Efficiency. IEEE J. Solid-State Circuits 25(5), 1217–1225 (1990)

Tau, E., et al.: A First Generation FPGA Implementation. In: Workshop Proc. on FPD, Montreal, pp. 138–143 (1995)

Stansfield, A., Page, I.: The Design of a New FPGA Architecture. In: Proc. in Field- Programmable Logic and Applications, Univ. of Oxford, London (1995)

Altera Corporation, APEX20K PLD Family Data Sheet (2004)

Xilinx Corporation, Virtex-E Platform FPGAs Complete Data Sheet (2005)

He, J., Rose, J.: Advantages of Heterogeneous Logic Block Architectures for FPGAs. In: Proc. in Custom Integrated Circuits, San Diego, pp. 7.4.1–7.4.5 (1993)

Kouloheris, J.L., El Gamal, A.: PLA-based FPGA Area vs. Cell Granularity. In: Proceedings of the Custom Integrated Circuits Conference (1992)

Wilton, S., Rose, J., Vranesic, Z.: Architecture of Centralized Field-Configurable Memory. In: ACM International Symposium on FPGA, Monterey Bay, CA (1995)

Nadjarbashi, M., Fakhraia, S.M., et al.: On routing architecture for Hybrid architecture. Scientia Iranica 11(3), 159–164 (2004)

Singh, S.K., et al.: System level Architectural Synthesis & Compilation Technique in Reconfigurable Computing System. In: ESA 2010, USA, pp. 109–115 (2010)

Singh, S.K., et al.: IJCA 24(4), 50–54 (2011)

Brown, S., Rose, J.: Architecture of FPGAs and CPLDs: A Tutorial. University of Toronto

Hamblen, J.O., Hall, T.S., Furman, M.D.: Rapid prototyping of digital systems - Quartus II ed. Springer Book (2006)

Li-Guang, et al: A Novel Hybrid FPGA Architecture. IEEE (2006)

Cong, J.: FlowMap: An Optimal Technology Mapping Algorithm for Delay optimization in LUTbased FPGA Designs. IEEE Transaction on CAD 13(1) (1994)

Yang, S.: Logic Synthesis and Optimization Benchmarks, Version 3.0. Tech. Report, Microelectronics Center of North Carolina (1991)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2013 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Singh, S.K., Singh, R.K., Bhatia, M.P.S., Singh, S.P. (2013). CAD for Delay Optimization of Symmetrical FPGA Architecture through Hybrid LUTs/PLAs. In: Meghanathan, N., Nagamalai, D., Chaki, N. (eds) Advances in Computing and Information Technology. Advances in Intelligent Systems and Computing, vol 178. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-31600-5_57

Download citation

DOI: https://doi.org/10.1007/978-3-642-31600-5_57

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-31599-2

Online ISBN: 978-3-642-31600-5

eBook Packages: EngineeringEngineering (R0)