Abstract

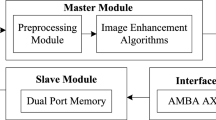

This paper proposed an image processing system based on hardware accelerator design method in FPGA chip. The architectures of the image system will be described. A hardware accelerator for scaling image is designed with Avalon-MM burst mode in System-on-a-Programmable-Chip (SOPC). There is a human-machine interface which display on the LCD Touch Panel Module (LTM) is designed in the image processing system. A user can choose a scaling factor by touching screen panel, and then LTM will display a 640 × 480 image on the LTM screen. Finally, the experimental result shows the comparison of the two design methods, and the hardware accelerator has better performance than Nios II processor.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Li, S.A., Liu, T.K., Chen, K.Y., Wong, C.C.: The Design of Embedded Real-time Image Processing Platform Based on SOPC Technique. Journal of Harbin Institute of Technology 18(1), 328–333 (2011)

Wang, Z., Ning, N.: A Image Capture And Storage System Based on SOPC. In: 2010 3rd International Congress on Image and Signal Processing (CISP), Yantai, pp. 1999–2002 (2010)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2012 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Li, SA., Wong, CC., Yang, CY., Chen, LF. (2012). Hardware Accelerator Design for Image Processing. In: Herrmann, G., et al. Advances in Autonomous Robotics. TAROS 2012. Lecture Notes in Computer Science(), vol 7429. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-32527-4_48

Download citation

DOI: https://doi.org/10.1007/978-3-642-32527-4_48

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-32526-7

Online ISBN: 978-3-642-32527-4

eBook Packages: Computer ScienceComputer Science (R0)