Abstract

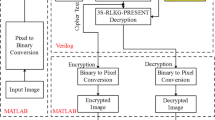

In this paper, DES algorithm is implemented by applying pipelining concept to the key scheduling part. Using this implementation, it is possible to have the key length equal to data length; which further improves the security of the system, at the same time decaying the performance. This scenario is similar to that of one time pad. i.e, here key storage and transmission is going to occupy more area and power, degrading the performance of the system. The security vs performance trade off is analyzed for the circuit. Another solution is also introduced in this paper, i.e, the Linear Feedback Shift Registers(LFSRs). Using LFSR, it is possible to have different keys generated every clock cycles, improving the security of the system, at the same time we need to store or transmit the single seed of LFSR only. The design is implemented in Virtex 5 FPGA device using Xilinx 12.1 platform. An encryption rate of 35.5 gbits/S is obtained, which is almost the fastest among all other current implementations. The performance of the system in terms of area, power and timing is analyzed using the Synopsys tool.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Leonard, J., Mangione-Smith, W.H.: A Case Study of Partially Evaluated Hardware Circuits: Key-Specific DES. In: Glesner, M., Luk, W. (eds.) FPL 1997. LNCS, vol. 1304, pp. 151–160. Springer, Heidelberg (1997)

Van Der Lubbe, J.C.A.: Basic methods of cryptography. Cambridge University Press (1998)

Menezes, A., Oorschot, P., Vanstone, S.: Handbook of applied cryptography. CRC Press (1117)

McLoone, M., McCanny, J.: High-performance FPGA implementation of DES using a novel method for implementing the key schedule. IEE Proc.: Circuits, Devices & Systems 150, 373–378 (2003)

McLoone, M., McCanny, J.V.: Data encryption apparatus. UK Patent Application 0023409.6 (October 2000)

Wong, K., Wark, M., Dawson, E.: A single-chip FPGA implementation of the data encryption standard (DES) algorithm. In: Proc. IEEE Globecom Communications Conf., Sydney, Australia, pp. 827–832 (November 1998)

Biham, E.: A Fast New DES Implementation in Software. In: Biham, E. (ed.) FSE 1997. LNCS, vol. 1267, pp. 260–272. Springer, Heidelberg (1997)

Kaps, J.-P., Paar, C.: Fast DES Implementations for FPGAs and Its Application to a Universal Key-Search Machine. In: Tavares, S., Meijer, H. (eds.) SAC 1998. LNCS, vol. 1556, pp. 234–247. Springer, Heidelberg (1999)

Free-DES Core (March 2000), http://www.free-ip.com/DES/

Wilcox, D.C., Pierson, L.G., Robertson, P.J., Witzke, E.L., Gass, K.: A DES ASIC Suitable for Network Encryption at 10 Gbps and Beyond. In: Koç, Ç.K., Paar, C. (eds.) CHES 1999. LNCS, vol. 1717, pp. 37–48. Springer, Heidelberg (1999)

Patterson, C.: High performance DES encryption in virtex FPGAs using Jbits. In: Proc. IEEE Symp. on Field-Programmable Custom Computing Machines, FC 2000, Napa Valley, CA, USA, pp. 113–121. IEEE Comput. Soc., CA (2000)

Patel, V., Joshi, R.C., Saxena, A.K.: FPGA implementation of DES using pipelining Concept with skew core key-scheduling

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2012 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Sruthi, P.V., Poornachandran, P., Remya Ajai, A.S. (2012). Performance Analysis and Improvement Using LFSR in the Pipelined Key Scheduling Section of DES. In: Thampi, S.M., Zomaya, A.Y., Strufe, T., Alcaraz Calero, J.M., Thomas, T. (eds) Recent Trends in Computer Networks and Distributed Systems Security. SNDS 2012. Communications in Computer and Information Science, vol 335. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-34135-9_22

Download citation

DOI: https://doi.org/10.1007/978-3-642-34135-9_22

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-34134-2

Online ISBN: 978-3-642-34135-9

eBook Packages: Computer ScienceComputer Science (R0)