Abstract

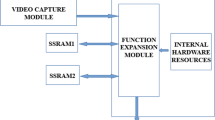

A high-level Field Programmable Gate Array (FPGA) prototype for a JPEG image encoder has been developed by the Structures, Pointing, and Control Engineering (SPACE) University Research Center (URC). The FPGA prototype uses MathWorks Simulink and Xilinx System Generator for deployment on its Virtex-5 FPGA board. The FPGA module serves as a co-processor of a real-time Ubiquitous Video Conferencing (UVC) software package. The project objective is to: 1) study the high-level synthesis method for FPGA design, and 2) provide the digital signal processing necessary to offload computationally-intensive video processing data from a host computer running the UVC application [1]. The project uses a Xilinx XUPV5-LV110T FPGA Development System. The image compression utilizes the JPEG standard. Each module for the JPEG encoder is designed in Simulink. To reduce computation time on the FPGA due to floating-point Discrete Cosine Transform (DCT) calculations, a table containing DCT cosine product values was computed in Excel, accurate to two decimal digits. These values are shifted 6 bits to the left to maintain accuracy and loaded onto the FPGA. The product of 8-bit YCbCr channel data and tabulated values is accumulated into a register, then scaled and shifted 6 bits to the right to complete the DCT.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Structures, propulsion, and control engineering space center, California State University, Los Angeles (2012), http://www.calstatela.edu/orgs/space/

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2013 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Nunez, G. et al. (2013). High Level FPGA Modeling of an JPEG Encoder. In: Brisk, P., de Figueiredo Coutinho, J.G., Diniz, P.C. (eds) Reconfigurable Computing: Architectures, Tools and Applications. ARC 2013. Lecture Notes in Computer Science, vol 7806. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-36812-7_27

Download citation

DOI: https://doi.org/10.1007/978-3-642-36812-7_27

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-36811-0

Online ISBN: 978-3-642-36812-7

eBook Packages: Computer ScienceComputer Science (R0)