Abstract

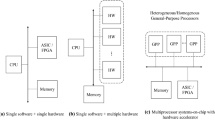

Power efficiency is a critical constraint for embedded systems. To address this many technological innovations are being proposed by the community. However, leveraging such advances also requires algorithmic solutions to handle the potential for run-time errors due to near threshold computing. In this work we plan to develop algorithmic innovations and optimizations for power efficiency in the emerging landscape of embedding computing platforms. We also plan to develop resilient run-time systems and incorporate resiliency in algorithmic solutions. In this paper we briefly describe our design methodology employed in the TAPAS (Tunable Algorithms for PERFECT Architectures) project. The TAPAS project is funded under the DARPA PERFECT (Power Efficiency Revolution for Embedded Computing Technologies) program.

This work has been funded by DARPA under grant number HR0011-12-2-0023.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Prasanna, V.K.: Energy-Efficient Computations on FPGAs. J. Supercomput. 32(2), 139–162 (2005)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2013 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Matam, K.K., Prasanna, V.K. (2013). Algorithm Design Methodology for Embedded Architectures. In: Brisk, P., de Figueiredo Coutinho, J.G., Diniz, P.C. (eds) Reconfigurable Computing: Architectures, Tools and Applications. ARC 2013. Lecture Notes in Computer Science, vol 7806. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-36812-7_31

Download citation

DOI: https://doi.org/10.1007/978-3-642-36812-7_31

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-36811-0

Online ISBN: 978-3-642-36812-7

eBook Packages: Computer ScienceComputer Science (R0)