Abstract

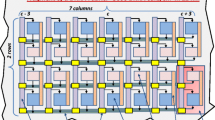

Partial dynamic reconfigurable (PDR) systems designed with state-of-the-art tool chains, like the Early Access Partial Reconfiguration (EAPR) Flow from Xilinx, does not exploit the full flexibility and all features which a state of the art FPGA chip offers. For example the utilized chip area and the position of a region which can be reconfigured dynamically is traditionally specified during design-time. Thereby the shape and the size of the reconfigurable area are set by the size of the largest module to be reconfigured. The consequence is that if a smaller module is placed on that region, chip area stays unused as so called black silicon. This drawback is only one example for the limitation of development tools of reconfigurable hardware architectures. In this book section, a new approach for exploiting the capability of reconfigurable hardware architectures is presented. It allows exploiting the reconfigurable architectures more efficient than other solutions introduced before. This is achieved through a novel concept of using micro blocks for the communication infrastructure as well as for the functional elements on the FPGA. The granularity and the online versus offline tradeoff for the usage of the micro blocks for building up more complex structures on the FPGA will be presented in this chapter.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Xilinx, Early access partial reconfiguration user guide, ug208. http://www.xilinx.com. Accessed Mar 2005

Benini L, De Micheli G (2002) Networks on chip: a new paradigm for systems on chip design. In: Proceedings of Design, automation and test in Europe conference and exhibition, pp 418–419

Braun L, Goehringer D, Perschke T, Schatz V, Huebner M, Becker J (2008) Adaptive real-time image processing exploiting two dimensional reconfigurable architecture. J Real-Time Image Process. http://dx.doi.org/10.1007/s11554-008-0095-8

Huebner M, Braun L, Becker J, Claus C, Stechele W (2007) Physical configuration on-line visualization of xilinx virtex-ii fpgas. In: Proceedings of IEEE computer society annual symposium on VLSI ISVLSI, 07, pp 41–46, 9–11 Mar 2007

Xilinx, Logicore ip xps hwicap (v5.00a), Access, 2010

Claus C, Zhang B, Stechele W, Braun L, Hubner M, Becker J (2008) A multi-platform controller allowing for maximum dynamic partial reconfiguration throughput. In: Proceedings international conference on field programmable logic and applications FPL 2008, pp 535–538

Hubner M, Gohringer D, Noguera J, Becker J (2010) Fast dynamic and partial reconfiguration data path with low hardware overhead on xilinx fpgas, 2010 IEEE international symposium on parallel and distributed processing, workshops and PhD forum (IPDPSW), pp 1–8 http://ieeexplore.ieee.org/lpdocs/epic03/wrapper.htm?arnumber=5470736

Huebner M, Schuck C, Kuehnle M, Becker J (2006) New 2-dimensional partial dynamic reconfiguration techniques for real-time adaptive microelectronic circuits. In: Schuck C (ed) Proceedings of IEEE Computer society annual symposium on emerging VLSI technologies and architectures, p 6

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2011 Springer Science+Business Media B.V.

About this paper

Cite this paper

Braun, L., Becker, J. (2011). Two Dimensional Dynamic Multigrained Reconfigurable Hardware. In: Voros, N., Mukherjee, A., Sklavos, N., Masselos, K., Huebner, M. (eds) VLSI 2010 Annual Symposium. Lecture Notes in Electrical Engineering, vol 105. Springer, Dordrecht. https://doi.org/10.1007/978-94-007-1488-5_18

Download citation

DOI: https://doi.org/10.1007/978-94-007-1488-5_18

Published:

Publisher Name: Springer, Dordrecht

Print ISBN: 978-94-007-1487-8

Online ISBN: 978-94-007-1488-5

eBook Packages: EngineeringEngineering (R0)