Abstract

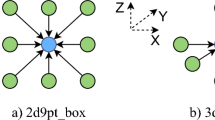

Stencil computations are a class of computational kernels which update array elements according to some stencil patterns, and they have drawn more attentions recently. The Intel Xeon Phi coprocessor, which is designed for high performance computing, has not been fully evaluated for stencil computations. In this paper, we present a series of optimizations to accelerate the 3-D 7-point stencil code on Intel Xeon Phi coprocessor. We focus on how to exploit the performance potential of many cores and wide-vector unit in each core. In order to exploit data locality, we use loop tiling and we propose a method for calculating the block size while tiling. The achieved performance brings a speedup of 211.6 in comparison with the serial code.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

HiStencils. http://www.exastencils.org/histencils/. Accessed 15 Apr 2015

Stencil code. http://en.wikipedia.org/wiki/Stencil_code/. Accessed 15 Apr 2015

Michael, M., Reinders, J., Robison, A.: Structured Parallel Programming: Patterns for Efficient Computation. Elsevier, Amsterdam (2012)

Intel Corporation. Intel\(^{\textregistered }\) Xeon Phi™ coprocessor system software developers guide, March 2014

Duran, A., Michael, K.: The Intel\(^{\textregistered }\) many integrated core architecture. In: International Conference on High Performance Computing and Simulation (HPCS). IEEE (2012)

James, J., Reinders, J.: Intel\(^{\textregistered }\) Xeon Phi™ Coprocessor High-performance Programming. Newnes, Oxford (2013)

Top 500 list. http://www.top500.org/. Accessed 1 June 2016

Chapman, B., Jost, G., Van Der Pas, R.: Using OpenMP: Portable Shared Memory Parallel Programming, vol. 10. MIT press, Massachusetts (2008)

Xue, J.: Loop Tiling for Parallelism. Springer Science & Business Media, Berlin (2000)

Leopold, C.: Tight bounds on capacity misses for 3D stencil codes. In: Sloot, P.M.A., Tan, C.J.K., Dongarra, J., Hoekstra, A.G. (eds.) ICCS-ComputSci 2002, Part I. LNCS, vol. 2329, pp. 843–852. Springer, Heidelberg (2002)

Schäfer, A., Fey, D.: High performance stencil code algorithms for GPGPUs. Procedia Comput. Sci. 4, 2027–2036 (2011)

Maruyama, N., Takayuki, A.: Optimizing stencil computations for NVIDIA Kepler GPUs. In: Proceedings of the 1st International Workshop on High Performance Stencil Computations, Vienna (2014)

You, Y., et al.: Evaluating multi-core, many-core architectures through accelerating the three-dimensional LaxCWendroff correction stencil. Int. J. High Perform. Comput. Appl. 28(3), 301–318 (2014)

Rahman, S.M., Faizur, Q.Y., Apan, Q.: Understanding stencil code performance on multicore architectures. In: Proceedings of the 8th ACM International Conference on Computing Frontiers. ACM (2011)

Wang, Q., et al.: Accelerating embarrassingly parallel algorithm on Intel MIC. In: International Conference on Progress in Informatics and Computing (PIC). IEEE (2014)

Tao, G., et al.: Using the intel many integrated core to accelerate graph traversal. Int. J. High Perform. Comput. Appl. 28(3), 255–266 (2014)

Acknowledgments

The work described in this paper is partially supported by the project of National Science Foundation of China under grant No.61170046 and No.61402495.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2016 Springer Science+Business Media Singapore

About this paper

Cite this paper

Feng, L., Dong, Y., Li, C., Jiang, H. (2016). High Performance Stencil Computations for Intel\(^{\normalsize \circledR }\) Xeon Phi™ Coprocessor. In: Wu, J., Li, L. (eds) Advanced Computer Architecture. ACA 2016. Communications in Computer and Information Science, vol 626. Springer, Singapore. https://doi.org/10.1007/978-981-10-2209-8_10

Download citation

DOI: https://doi.org/10.1007/978-981-10-2209-8_10

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-10-2208-1

Online ISBN: 978-981-10-2209-8

eBook Packages: Computer ScienceComputer Science (R0)