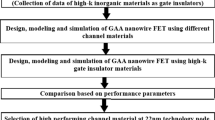

Abstract

In sub 10 nm technology node, vertical silicon nanowire (VNW) FET device has become a promising substitute due to its better gate controllability, short channel immunity, high ION/IOFF ratio and CMOS compatibility. This paper presents, a standard cell library using physics based Verilog-A compact model for 10 nm vertical SiNW FET device. A unified compact model included all the nanoscale effects (e.g. short channel effects, mobility degradation, velocity saturations etc.) as well as the parasitic capacitance and resistance model, which are highly dominant in lower technology nodes. The compact model is well matched with TCAD simulation data at 10 nm VNW FET device level. The cell library builds comprises of INVERTER, NAND, NOR and Ex-OR gate cells. Further, we compared the 10 nm VNW FET based standard cell performance to 45 nm bulk CMOS based standard cell library. It is found that the VNWFET based cells library design have an advantage of delay by ~4X and power consumption by ~14X against the 45 nm CMOS technology.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Goel, E., Kumar, S., Singh, K., Singh, B., Kumar, M., Jit, S.: 2-D analytical modeling of threshold voltage for graded-channel dual-material double-gate MOSFETs. IEEE Trans. Electron Devices 63(3), 966–973 (2016)

Sharma, M., Maheshwaram, S., Prakash, O., Bulusu, A., Saxena, A.K., Manhas, S.K.: Compact model for vertical silicon nanowire based device simulation and circuit design. In: ISOCC, pp. 107–108 (2015)

Maheshwaram, S., Manhas, S.K., Kaushal, G., Anand, B., Singh, N.: Vertical nanowire CMOS parasitic modeling and its performance analysis. IEEE Trans. Electron Devices 60(9), 2943–2950 (2013)

Xie, Q., Lin, X., Wang, Y., Dousti, M.J., Shafaei, A., Ghasemi-Gol, M., Pedram, M.: 5 nm FinFET standard cell library optimization and circuit synthesis in near-and super-threshold voltage regimes. In: Proceedings of the IEEE Computer Society Annual Symposium on VLSI, ISVLSI, pp. 424–429 (2014)

Xie, Q., Lin, X., Wang, Y., Chen, S., Dousti, M.J., Pedram, M.: Performance comparisons between 7-nm FinFET and conventional bulk CMOS standard cell libraries. IEEE Trans. Circuits Syst. II Express Briefs 62(8), 761–765 (2015)

Prakash, O., Sharma, M., Bulusu, A.: Lateral silicon nanowire based standard cell design for higher performance. In: APCCAS, vol. 2, pp. 135–138 (2016)

16 nm PTM-MG. http://ptm.asu.edu/

Cui, T., Xie, Q., Wang, Y., Nazarian, S., Pedram, M.: 7 nm FinFET standard cell layout characterization and power density prediction in near- and super-threshold voltage regimes. In: 2014 International Green Computing Conference IGCC (2015)

Acknowledgements

We Dr. Satish Maheshwaram and Mr. Mohit Sharma, would like to thank our co-author Mr. Om Prakash and our supervisors Dr. Anand Bulusu, Dr. Sanjeev Manhas who have redone the work (after our graduation) on standard cell library delay and power analysis at Indian Institute of Technology Roorkee to make this a better research work.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2017 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Maheshwaram, S., Prakash, O., Sharma, M., Bulusu, A., Manhas, S. (2017). Vertical Nanowire FET Based Standard Cell Design Employing Verilog-A Compact Model for Higher Performance. In: Kaushik, B., Dasgupta, S., Singh, V. (eds) VLSI Design and Test. VDAT 2017. Communications in Computer and Information Science, vol 711. Springer, Singapore. https://doi.org/10.1007/978-981-10-7470-7_24

Download citation

DOI: https://doi.org/10.1007/978-981-10-7470-7_24

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-10-7469-1

Online ISBN: 978-981-10-7470-7

eBook Packages: Computer ScienceComputer Science (R0)