Abstract

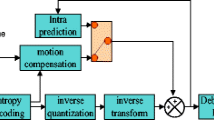

This paper describes the hardware design of 4 × 4 block-based Sample Adaptive Offset (SAO) for high-performance HEVC. The HEVC in-loop filter consists of a deblocking filter and SAO. SAO is used to compensate for errors in image compression. However, it has a high latency due to pixel-based computation. The proposed hardware architecture performs 4 × 4 block-based operations and has high throughput through a two-stage pipeline. The offset operation module minimizes the hardware area by using the adder and the right shift operations. The proposed hardware architecture is synthesized using a 65 nm cell library. The maximum operating frequency is 312.5 MHz and the total number of gates is 193.6 k.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Sullivan GJ, Ohm JR, Han WJ, Wiegand T (2012) Overview of the high efficiency video coding (HEVC) standard. IEEE Trans Circ Syst Video Technol 22(12):1649–1668

Fu C, Alshina E, Alshin A, Huang Y, Chen C, Tsai C, Hsu C, Lei S, Park J, Han W (2012) Sample adaptive offset in the HEVC standard. IEEE Trans Circ Syst Video Technol 22(12):1755–1764

Choi Y, Joo J (2015) Exploration of practical HEVC/H.265 sample adaptive offset encoding policies. IEEE Signal Process Lett 22(4):465–468

Zhou J, Zhou D, Wang S, Zhang S, Yoshimura T, Goto S (2017) A dual-clock VLSI design of H.265 sample adaptive offset estimation for 8k Ultra-HD TV encoding. IEEE Trans Very Large Scale Integr VLSI Syst 25(2):714–724

Shen W, Fan Y, Bai Y, Huang L, Shang Q, Liu C, Zeng X (2016) A combined deblocking filter and SAO hardware architecture for HEVC. IEEE Trans Multimedia 18(6):1022–1033

Shukla K, Swamy B, Rangababu P (2017) Area efficient dataflow hardware design of SAO filter for HEVC. In: 2017 international conference on innovations in electronics, signal processing and communication (IESC), pp 16–21

Acknowledgements

This research was supported by the MSI (Ministry of Science, ICT and Future Planning), Korea, under the Global IT Talent support program (IITP-2017-0-01681) and Human Resource Development Project for Brain scouting program (IITP-2016-0-00352) supervised by the IITP (Institute for Information and Communication Technology Promotion).

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2019 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Park, S., Ryoo, K. (2019). Hardware Design of HEVC In-Loop Filter for Ultra-HD Video Encoding. In: Park, J., Loia, V., Choo, KK., Yi, G. (eds) Advanced Multimedia and Ubiquitous Engineering. MUE FutureTech 2018 2018. Lecture Notes in Electrical Engineering, vol 518. Springer, Singapore. https://doi.org/10.1007/978-981-13-1328-8_52

Download citation

DOI: https://doi.org/10.1007/978-981-13-1328-8_52

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-13-1327-1

Online ISBN: 978-981-13-1328-8

eBook Packages: EngineeringEngineering (R0)