Abstract

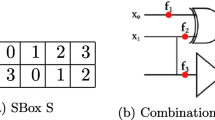

The study of Hardware Trojan and its impact is a cutting edge research topic today. Hardware Trojan Horses (HTH) are inserted by an adversary either during design or fabrication phase of IC which does the malicious alterations in the circuit. The main objective of this paper is to insert two new hardware Trojan designs on cryptosystem and study its impact by calculating path delay, power consumption and area utilization. In particular, the proposed Trojan is designed using single trigger with multiple payloads structure. These designs are imposed to do the malicious action of fault injection on the penultimate mixcolumn of AES-128, which enables to extract the entire 128 bit secret key with minimum time of activation on the HTHs by performing Differential Fault Analysis (DFA). Both the Trojan inserted AES designs are implemented on the Xilinx Virtex-5 FPGAs. The proposed Trojan designs, HT1 and HT2 have minimal area overhead of 0.7% and 1.5% respectively with frequency overhead of 2% each. Provided, the models designed have a negligible effect on path delay and power consumption when compared to the original AES.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Abusaidi, P., Klein, M., Philofsky, B.: Virtex-5 FPGA System Power Design Considerations, Xilinx White Paper WP285 (v1.0), 14 February 2008

Agrawal, D., Baktir, S., Karakoyunlu, D., Rohatgi, P., Sunar, B.: Trojan detection using IC fingerprinting. In: IEEE Symposium on Security and Privacy (SP 2007), pp. 296–310, May 2007

Alkabani, Y., Koushanfar, F.: Consistency-based characterization for IC Trojan detection. In: IEEE/ACM International Conference on Computer-Aided Design - Digest of Technical Papers, pp. 123–127, November 2009

Anandakumar, N.N., Dillibabu, S.: Correlation power analysis attack of AES on FPGA using customized communication protocol. In: Proceedings of the Second International Conference on Computational Science, Engineering and Information Technology, CCSEIT 2012, pp. 683–688 (2012)

Bhasin, S., Danger, J.L., Guilley, S., Ngo, X.T., Sauvage, L.: Hardware Trojan Horses in cryptographic IP cores. In: Workshop on Fault Diagnosis and Tolerance in Cryptography, pp. 15–29, August 2013

Blömer, J., Seifert, J.-P.: Fault based cryptanalysis of the advanced encryption standard (AES). In: Wright, R.N. (ed.) FC 2003. LNCS, vol. 2742, pp. 162–181. Springer, Heidelberg (2003). https://doi.org/10.1007/978-3-540-45126-6_12

Boneh, D., DeMillo, R.A., Lipton, R.J.: On the importance of checking cryptographic protocols for faults. In: Fumy, W. (ed.) EUROCRYPT 1997. LNCS, vol. 1233, pp. 37–51. Springer, Heidelberg (1997). https://doi.org/10.1007/3-540-69053-0_4

Bulens, P., Standaert, F.-X., Quisquater, J.-J., Pellegrin, P., Rouvroy, G.: Implementation of the AES-128 on Virtex-5 FPGAs. In: Vaudenay, S. (ed.) AFRICACRYPT 2008. LNCS, vol. 5023, pp. 16–26. Springer, Heidelberg (2008). https://doi.org/10.1007/978-3-540-68164-9_2

Infosecurity: The stealthy Hardware Trojan that can affect INTEL IVY Bridge processor (2013). https://www.infosecurity-magazine.com/news/the-stealthy-hardware-trojan-that/

Jin, Y., Makris, Y.: Hardware Trojan detection using path delay fingerprint. In: IEEE International Workshop on Hardware-Oriented Security and Trust, pp. 51–57, June 2008

Karunakaran, D.K., Mohankumar, N.: Malicious combinational Hardware Trojan detection by gate level characterization in 90 nm technology. In: Fifth International Conference on Computing, Communications and Networking Technologies (ICCCNT), pp. 1–7, July 2014

Kasper, M., et al.: Side channels as building blocks. J. Cryptographic Eng. 2(3), 143–159 (2012)

Kocher, P., Jaffe, J., Jun, B.: Differential power analysis. In: Wiener, M. (ed.) CRYPTO 1999. LNCS, vol. 1666, pp. 388–397. Springer, Heidelberg (1999). https://doi.org/10.1007/3-540-48405-1_25

Plusquellic, J., Saqib, F.: Detecting Hardware Trojans using delay analysis. In: Bhunia, S., Tehranipoor, M.M. (eds.) The Hardware Trojan War, pp. 219–267. Springer, Cham (2018). https://doi.org/10.1007/978-3-319-68511-3_10

Potkonjak, M., Nahapetian, A., Nelson, M., Massey, T.: Hardware Trojan Horse detection using gate-level characterization. In: 46th ACM/IEEE Design Automation Conference, pp. 688–693, July 2009

Quisquater, J.-J., Samyde, D.: ElectroMagnetic Analysis (EMA): measures and counter-measures for smart cards. In: Attali, I., Jensen, T. (eds.) E-smart 2001. LNCS, vol. 2140, pp. 200–210. Springer, Heidelberg (2001). https://doi.org/10.1007/3-540-45418-7_17

Salmani, H., Tehranipoor, M., Plusquellic, J.: A layout-aware approach for improving localized switching to detect Hardware Trojans in integrated circuits. In: IEEE International Workshop on Information Forensics and Security, pp. 1–6, December 2010

Joye, M., Tunstall, M. (eds.): Fault Analysis in Cryptography. Information Security and Cryptography, p. 356. Springer, Heidelberg (2012). https://doi.org/10.1007/978-3-642-29656-7

Vaddi, E., Gaddam, K., Maniam, R.K., Mallavajjala, S.A., Dasari, S., Nirmala Devi, M.: Detection and diagnosis of Hardware Trojan using power analysis. In: Abawajy, J.H., Mukherjea, S., Thampi, S.M., Ruiz-Martínez, A. (eds.) SSCC 2015. CCIS, vol. 536, pp. 519–529. Springer, Cham (2015). https://doi.org/10.1007/978-3-319-22915-7_47

Author information

Authors and Affiliations

Corresponding authors

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2019 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Manivannan, S., Nalla Anandakumar, N., Nirmala Devi, M. (2019). Key Retrieval from AES Architecture Through Hardware Trojan Horse. In: Thampi, S., Madria, S., Wang, G., Rawat, D., Alcaraz Calero, J. (eds) Security in Computing and Communications. SSCC 2018. Communications in Computer and Information Science, vol 969. Springer, Singapore. https://doi.org/10.1007/978-981-13-5826-5_37

Download citation

DOI: https://doi.org/10.1007/978-981-13-5826-5_37

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-13-5825-8

Online ISBN: 978-981-13-5826-5

eBook Packages: Computer ScienceComputer Science (R0)