Abstract

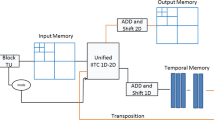

High Efficiency Video Coding (HEVC) is a new international video compression standard offering much better compression efficiency than previous video compression standards at the expense of much higher computational complexity. This paper presents a design of two-dimensional (2D) discrete cosine transform (DCT) hardware architecture dedicated for High Efficiency Video Coding (HEVC) in field programmable gate array (FPGA) platforms. The proposed methodology efficiently proceeds 2D-DCT computation to fit internal components and characteristics of FPGA resources. This architecture supports variable size of DCT computation, including 4 × 4, 8 × 8, 16 × 16, and 32 × 32, and has been implemented in Verilog and synthesized in various FPGA platforms. Compared with existing related works, our proposed architecture demonstrates significant advantages in the performance improvement with low FPGA resource utility, which are very important for the whole FPGA solution for whole HEVC codec.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Meuel, H., Munderloh, M., Ostermann, J.: Stereo mosaicking and 3D video for singleview HDTV aerial sequences using a low bit rate ROI coding framework. In: International Conference on Advanced Video and Signal Based Surveillance, pp. 1–6 (2015)

Bhaskaranand, M., Gibson, J.: Low-complexity video encoding for UAV reconnaissance and surveillance. In: Military Communications Conference, pp. 1633–1638 (2011)

Bhaskaranand, M., Gibson, J.: Low complexity video encoding and high complexity decoding for UAV reconnaissance and surveillance. In: International Symposium on Multimedia, pp. 163–170 (2013)

Zhang, Q., Chang, H., Huang, X., Huang, L., Su, R., Gan, Y.: Adaptive early termination mode decision for 3D-HEVC using inter-view and spatio-temporal correlations. Int. J. Electron. Commun. 70(5), 727–737 (2016)

Bossen, F., Bross, B., Suhring, K., Flynn, D.: HEVC complexity and implementation analysis. IEEE Trans. Circuits Syst. Video Technol. 22(12), 1685–1696 (2012)

Kalali, E., Ozcan, E., Yalcinkaya, O., Hamzaoglu, I.: A low energy HEVC inverse transform hardware. IEEE Trans. Consum. Electron. 60(4), 754–761 (2014)

Kessentini, A., Samet, A., Ayed, M., Masmoudi, N.: Performance analysis of inter-layer prediction module for H.264/SVC. Int. J. Electron. Commun. 69(1), 344–350 (2015)

Samcovic, A.: Mathematical modeling of coding gain and rate-distortion function in multihypothesis motion compensation for video signals. Int. J. Electron. Commun. 69(2), 487–491 (2015)

Budagavi, M., Fuldseth, A., Bjontegaard, G., Sze, V., Sadafale, M.: Core transform design in the high efficiency video coding (HEVC) standard. IEEE J. Selected Topics Signal Process. 7(6), 1029–1041 (2013)

Rao, K.R., Yip, P.: Discrete Cosine Transform: Algorithms, Advantages, Applications. Academic Press, Inc., Cambridge (1990)

Kalali, E., Mert, A.C., Hamzaoglu, I.: A computation and energy reduction technique for HEVC discrete cosine transform. IEEE Trans. Consum. Electron. 62(2), 166–174 (2016)

Conceicao, R., Souza, J., Jeske, R., Zatt, B., Porto, M., Agostini, L.: Low-cost and high throughput hardware design for the HEVC 16 × 16 2-D DCT transform. J. Integr. Circ. Syst. 9, 25–35 (2014)

Mert, A.C., Kalali, E., Hamzaoglu, I.: An FPGA implementation of future video coding 2D transform. In: IEEE International Conference on Consumer Electronics - Berlin. IEEE (2017)

Park, J.S., Nam, W.J., Han, S.M., et al.: 2-D large inverse transform (16 × 16, 32 × 32) for HEVC (High Efficiency Video Coding). J. Semicond. Technol. Sci. 12(2), 203–211 (2012)

Chen, T.H.: A cost-effective 8 × 8 2-D IDCT core processor with folded architecture. IEEE Trans. Consum. Electron. 45(2), 333–339 (1999)

Sjovall, P., Viitamaki, V., Vanne, J., et al.: High-level synthesis implementation of HEVC 2-D DCT/DST on FPGA. In: IEEE International Conference on Acoustics. IEEE (2017)

Huang, J., Parris, M., Lee, J., et al.: Scalable FPGA architecture for DCT computation using dynamic partial reconfiguration. ACM Trans. Embedded Comput. Syst. 9(1), 269–272 (2009)

Chen, M., Zhang, Y., Lu, C.: Efficient architecture of variable size HEVC 2D-DCT for FPGA platforms. Aeu Int. J. Electron. Commun. 73, 1–8 (2017)

Mert, A.C., Kalali, E., Hamzaoglu, I.: An FPGA implementation of future video coding 2D transform. In: IEEE International Conference on Consumer Electronics - Berlin. IEEE (2017)

Acknowledgments

We acknowledge the reviewers for their insightful comments. This work is supported by the HGJ2017 under Grant No.2017ZX01028103 and Grant 2018ZX01029103.

Author information

Authors and Affiliations

Corresponding authors

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2020 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Zhang, Y., Li, G., Wang, L. (2020). A High-Performance with Low-Resource Utility FPGA Implementation of Variable Size HEVC 2D-DCT Transform. In: Dong, D., Gong, X., Li, C., Li, D., Wu, J. (eds) Advanced Computer Architecture. ACA 2020. Communications in Computer and Information Science, vol 1256. Springer, Singapore. https://doi.org/10.1007/978-981-15-8135-9_24

Download citation

DOI: https://doi.org/10.1007/978-981-15-8135-9_24

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-15-8134-2

Online ISBN: 978-981-15-8135-9

eBook Packages: Computer ScienceComputer Science (R0)