Abstract

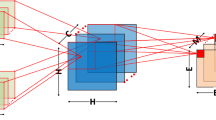

In recent years, the design of artificial intelligence computing system to improve system performance by hardware acceleration has become a trend. High bandwidth, highly compatible data stream for hardware operation flow is a key factor affecting hardware acceleration performance. Therefore, this paper proposes the Link-list DMAC (LDMAC), which can support the linked transfer of three-dimension data block access, high-flexibility data retrieval arrangement. Based on the design concept of establishing high-bandwidth data flow and highly flexible data acquisition, LDMAC has the following design. 1) DMA List: including multiple linked nodes (DMA List Node), each node can be configured with single/multiple channels and single/multiple map data block access mode, access data acquisition and arrangement rules, so as to the LDMAC design that realizes high flexibility and supports linked transfer. 2) PackUnpack Buffer (PUPB): the internal register of LDMAC, supporting highly flexible data arrangement. 3) ABP Buffer: a triple buffer structure with dual data buffers and prefetch data buffer. The buffer data storage and exchange mechanism according to the data access state can improve the storage efficiency of discontinuous data and improve the continuity of data flow. 4) Double-buffering Design: The Ping-Pong mechanism is applied to provide overlapping computing between the LDMAC and the acceleration hardware to improve the system operation performance. In this paper, a synthesizable LDMAC is implemented. With 40 nm library technology of TSMC, a working frequency of 250 MHz is achieved. In terms of simulation verification, by working collaboratively with the CNN accelerator, LDMAC can improve access efficiency by 63% compared to requesting data directly from DRAM.

This paper presents partial results of a long-term research project financed by both NSTC of R.O.C. under contract no. MOST 111-2218-E-110-004 and the industry.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Lecun, Y., Bottou, L., Bengio, Y., Haffner, P.: Gradient-based learning applied to document recognition. Proc. IEEE 86(11), 2278–2324 (Nov.1998). https://doi.org/10.1109/5.726791

Krizhevsky, A., Sutskever, I., Hinton, G.E.: ImageNet classification with deep convolutional neural networks. In: International Conference on Neural Information Processing Systems, pp. 1097–1105 (2013)

Simonyan, K., Zisserman, A.: Very deep convolutional networks for large-scale image recognition. In: Proceedings of International Conference on Learning Representations (2015)

Howard, A.G., et al.: MobileNets: efficient convolutional neural networks for mobile vision applications. arXiv:1704.04861 (2017) [online]. https://arxiv.org/abs/1704.04861

Kahle, J.A., Day, M.N., Hofstee, H.P., Johns, C.R., Maeurer, T.R., Shippy, D.: Introduction to the cell multiprocessor. IBM J. Res. Dev. 49(4.5,), 589–604 (2005)

Ma, G., He, H.: Design and implementation of an advanced DMA controller on AMBA-based SoC. In: 2009 IEEE 8th International Conference on ASIC, 2009, pp. 419–422 (2009). https://doi.org/10.1109/ASICON.2009.5351258

Ponsard, R., Janvier, N., Houzet, D., Fristot, V., Mansour, W.: Online GPUAnalysis using adaptive DMA controlled by softcore for 2D detectors. In: 2020 23rd Euromicro Conference on Digital System Design (DSD), pp. 436–439 (2020). https://doi.org/10.1109/DSD51259.2020.00075

Shirur, Y.J.M., Sharma, K.M.: Design and implementation of efficient direct memory access (DMA) controller in multiprocessor SoC. In: 2018 International Conference on Networking, Embedded and Wireless Systems (ICNEWS), pp. 1–6 (2018). https://doi.org/10.1109/ICNEWS.2018.8903991

Morales, H., Duran, C., Roa, E.: A low-area direct memory access controller architecture for a RISC-V based low-power microcontroller, In: 2019 IEEE 10th Latin American Symposium on Circuits & Systems (LASCAS), pp. 97–100 (2019). https://doi.org/10.1109/LASCAS.2019.8667579

Nguyen, H., Dong, K., Tran, X-T.: A reconfigurable multi-function DMA controller for high-performance computing systems, pp. 344–349 (2018). https://doi.org/10.1109/NICS.2018.8606841

Madhuri, R.A., Hampali, M.W., Umesh, N., Pooja, K.S., Shirur, Y.J.M., Chakravarthi, V.S.: Design and implementation of EDMA controller for AI based DSP SoCs for real-time multimedia processing. In: 2020 Fourth International Conference on I-SMAC (IoT in Social, Mobile, Analytics and Cloud) (I-SMAC), pp. 554–563 (2020). https://doi.org/10.1109/I-SMAC49090.2020.9243535

Kashimata, T., Kitamura, T., Kimura, K., Kasahara, H.: Cascaded DMA controller for speedup of indirect memory access in irregular applications. In: 2019 IEEE/ACM 9th Workshop on Irregular Applications: Architectures and Algorithms (IA3), pp. 71–76 (2019). https://doi.org/10.1109/IA349570.2019.00017

Ma, S., Huang, L., Lei, Y., Guo, Y., Wang, Z.: An efficient direct memory access (DMA) controller for scientific computing accelerators. IEEE International Symposium on Circuits and Systems (ISCAS) 2019, 1–5 (2019). https://doi.org/10.1109/ISCAS.2019.8702172

Ma, S., Lei, Y., Huang, L., Wang, Z.: MT-DMA: A DMA controller supporting efficient matrix transposition for digital signal processing. IEEE Access 7, 5808–5818 (2019). https://doi.org/10.1109/ACCESS.2018.2889558

Scatter-Gather DMA Controller Core: Quartus II Handbook Version 9.1, Vol. 5, November 2009

IPUG67 - Scatter-Gather Direct Memory Access Controller IP Core User Guide: Lattice Semiconductor, April 2015

JEDEC Solid State Technology Association (2012). DDR3 SDRAM Standard (JESD79-3F)

Gross. J.: High-performance DRAM system design constraints and considerations. Master's thesis, University of Maryland, College Park, August 2010

Chiu, J.-C., Su, K.L.: Design and Implementation of brain memory controller with cache memory. Master thesis, National Sun Yat-sen University, Kaohsiung (2021)

Chiu, J.-C., Yang, K.-M., Chou, Y.-L., Chih-Kang, W.: A relation-exchanging buffering mechanism for instruction and data streaming. Comput. Electr. Eng. Kaohsiung 39(4), 1129–1141 (2013)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2022 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Chiu, JC., Wu, YT., Liu, YC., Hsieh, CY. (2022). Design and Implementation of the Link-List DMA Controller for High Bandwidth Data Streaming. In: Hsieh, SY., Hung, LJ., Klasing, R., Lee, CW., Peng, SL. (eds) New Trends in Computer Technologies and Applications. ICS 2022. Communications in Computer and Information Science, vol 1723. Springer, Singapore. https://doi.org/10.1007/978-981-19-9582-8_41

Download citation

DOI: https://doi.org/10.1007/978-981-19-9582-8_41

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-19-9581-1

Online ISBN: 978-981-19-9582-8

eBook Packages: Computer ScienceComputer Science (R0)