Abstract

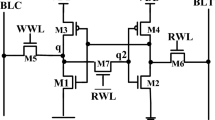

This paper presents a study and analysis of 10T SRAM (static random-access memory) cell and also comparison has been done with conventional 6T SRAM and it also gives good Read stability and Write Margin with 34.21% and 33.33% respectively and less power. Proposed design is used as a part of memory with single purpose devices which requires low power consumption and reliability because memories are integrated part of digital circuits. Analysis and design of this circuit is done by using cadence tool at 180 nm technology. Simulation-based results are represented in this paper.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Rukkumani, V., Saravanakumar, M., Srinivasan, K.: Design and analysis of SRAM cells for power reduction using low power techniques. 978-1-5090-2597-8/16/$31.00. IEEE (2016)

Upadhyay, P., Kar, R., Mandal, D., Ghoshal, S.P.: A novel IOT SRAM cell for low power circuits. 978-1-4799-3358-7114/$31.00. IEEE (2014)

Yan, H., Wang, D., Hou, C.: The design of low leakage SRAM cell with high SNM. 978-1-61284-193-9/11/$26.00. IEEE (2011)

Singh, S., Lakhmani, V.: Read and write stability of 6T SRAM. Int. J. Adv. Res. Electron. Commun. Eng. (IJARECE) 3(5) (2014)

Singh, P., Vishvakarma, S.K.: Ultra-low power high stability 8T SRAM for application in object tracking system. 216-3536 (2017)

Shiny Grace, P., Sivamangai, N.M.: Design of 10T SRAM cell for high SNM and low power. 978-1-5090-2309-7/16/$31.00. IEEE (2016)

Shivaprakash, G., Suresh, D.S.: Design of low power 6T-SRAM cell and analysis for high speed application. Indian J. Sci. Technol. 9(46) (2016). https://doi.org/10.17485/ijst/2016/v9i46/106144

Banga, H., Agarwal, D.: Single bit line 10T SRAM cell for low power and high SNM. In: Proceeding International Conference on Recent Innovations is Signal Processing and Embedded Systems (RISE - 2017), 27–29 October 2017

Priya, S., Gavaskar, K.: Design of efficient low power 9T SRAM cell. Int. J. Eng. Res. Technol. (IJERT) 2(1) (2013)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2019 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Singh, K., Gamad, R.S., Bansod, P.P. (2019). Design and Analysis for Power Reduction with High SNM of 10T SRAM Cell. In: Sengupta, A., Dasgupta, S., Singh, V., Sharma, R., Kumar Vishvakarma, S. (eds) VLSI Design and Test. VDAT 2019. Communications in Computer and Information Science, vol 1066. Springer, Singapore. https://doi.org/10.1007/978-981-32-9767-8_45

Download citation

DOI: https://doi.org/10.1007/978-981-32-9767-8_45

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-32-9766-1

Online ISBN: 978-981-32-9767-8

eBook Packages: Computer ScienceComputer Science (R0)