Abstract

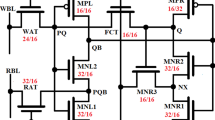

This paper presents a new write assist 12T SRAM cell with data dependent power supply with read decoupled circuit to enhance the read stability and write ability at the low supply voltage. The proposed 12T cell is design to isolate the read path for enhancing the read static noise margin. Stacking effect is used to control leakage current and improved write static noise margin of the cell. As compared with the 6T SRAM cell, the proposed cell offers 8.66\(\times \), 3.4\(\times \), and 1.53\(\times \) higher write, read and hold stability respectively at 0.4 V supply voltage. Our evaluation indicates that the leakage and write power of the proposed cell is reduced by 59% and 99.98% respectively as compared to the conventional 6T cell. For a better perspective of the proposed cell, a compound figure of merit has been introduced and it is found that the proposed cell has 38.048% higher FOM as compared to 6T SRAM cell. All the implementations have been performed using the industry standard 180 nm CMOS technology.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Calhoun, B.H., Chandrakasan, A.P.: Static noise margin variation for sub-threshold SRAM in 65-nm CMOS. IEEE J. Solid-State Circuits 41(7), 1673–1679 (2006)

Chuang, C.T., Mukhopadhyay, S., Kim, J.J., Kim, K., Rao, R.: High-performance SRAM in nanoscale CMOS: design challenges and techniques. In: IEEE International Workshop on Memory Technology, Design and Testing, MTDT 2007, pp. 4–12. IEEE (2007)

Kursun, V., Friedman, E.G.: Multi-voltage CMOS Circuit Design. Wiley, New York (2006)

Wen, L., Li, Z., Li, Y.: Single-ended, robust 8T SRAM cell for low-voltage operation. Microelectron. J. 44(8), 718–728 (2013)

Kushwah, C., Vishvakarma, S.K.: A single-ended with dynamic feedback control 8T subthreshold SRAM cell. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 24(1), 373–377 (2016)

Chang, I.J., Kim, J.J., Park, S.P., Roy, K.: A 32 kb 10T subthreshold SRAM array with bit-interleaving and differential read scheme in 90 nm CMOS. In: IEEE International Solid-State Circuits Conference, ISSCC 2008. Digest of Technical Papers, pp. 388–622. IEEE (2008)

Sharma, V., Gopal, M., Singh, P., Vishvakarma, S.K.: A 220 mV robust read-decoupled partial feedback cutting based low-leakage 9T SRAM for Internet of Things (IoT) applications. AEU-Int. J. Electron. Commun. 87, 144–157 (2018)

Sharma, V., Vishvakarma, S.K., Chouhan, S.S., Halonen, K.: A write-improved low-power 12T SRAM cell for wearable wireless sensor nodes. Int. J. Circuit Theory Appl. 46, 2314–2333 (2018)

Ahmad, S., Gupta, M.K., Alam, N., Hasan, M.: Single-ended Schmitt-trigger-based robust low-power SRAM cell. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 24(8), 2634–2642 (2016)

Lo, C.H., Huang, S.Y.: PPN based 10T SRAM cell for low-leakage and resilient subthreshold operation. IEEE J. Solid-State Circuits 46(3), 695–704 (2011)

Kim, J., Mazumder, P.: A robust 12T SRAM cell with improved write margin for ultra-low power applications in 40 nm CMOS. Integr. VLSI J. 57, 1–10 (2017)

Chiu, Y.W., et al.: 40 nm bit-interleaving 12T subthreshold SRAM with data-aware write-assist. IEEE Trans. Circuits Syst. I Regul. Pap. 61(9), 2578–2585 (2014)

Kulkarni, J.P., Roy, K.: Ultralow-voltage process-variation-tolerant schmitt-trigger-based SRAM design. IEEE Trans. VLSI Syst. 20(2), 319–332 (2012)

Chang, L., et al.: Stable SRAM cell design for the 32 nm node and beyond. In: 2005 Symposium on VLSI Technology. Digest of Technical Papers, pp. 128–129. IEEE (2005)

Sharma, V., Gopal, M., Singh, P., Vishvakarma, S.K., Chouhan, S.S.: A robust, ultra low-power, data-dependent-power-supplied 11T SRAM cell with expanded read/write stabilities for internet-of-things applications. Analog Integr. Circuits Signal Process. 98(2), 331–346 (2019)

Ahmad, S., Iqbal, B., Alam, N., Hasan, M.: Low leakage fully half-select-free robust SRAM cells with BTI reliability analysis. IEEE Trans. Device Mater. Reliab. 18(3), 337–349 (2018)

Seevinck, E., List, F.J., Lohstroh, J.: Static-noise margin analysis of MOS SRAM cells. IEEE J. Solid-State Circuits 22(5), 748–754 (1987)

van Santen, V.M., Martin-Martinez, J., Amrouch, H., Nafria, M.M., Henkel, J.: Reliability in super-and near-threshold computing: a unified model of rtn, bti, and pv. IEEE Trans. Circuits Syst. I Regul. Pap. 65(1), 293–306 (2018)

Acknowledgment

The authors would like to thank Special Manpower Development Program for Chips to System Design (SMDP-C2SD) research project of Department of Electronics and Information technology (DeitY) under Ministry of Communication and Information Technology, Government of India to provide the lab facilities.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2019 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Gupta, N., Prasad, J., Kumar, R.S., Rajput, G., Vishvakarma, S.K. (2019). A Robust Low-Power Write-Assist Data-Dependent-Power-Supplied 12T SRAM Cell. In: Sengupta, A., Dasgupta, S., Singh, V., Sharma, R., Kumar Vishvakarma, S. (eds) VLSI Design and Test. VDAT 2019. Communications in Computer and Information Science, vol 1066. Springer, Singapore. https://doi.org/10.1007/978-981-32-9767-8_52

Download citation

DOI: https://doi.org/10.1007/978-981-32-9767-8_52

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-32-9766-1

Online ISBN: 978-981-32-9767-8

eBook Packages: Computer ScienceComputer Science (R0)