Abstract

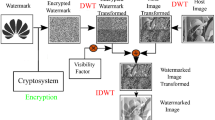

Entropy coding, as used for lossless compression in image coding, is dominated by serial bit processing on variable wordlength data. Digital signal processors (DSPs), in which pipeline processors play a central role, fail to yield adequate performance for this kind of application. This paper proposes a new approach that fulfills the two requirements for bit processing, the dominant task in entropy coding: high-performance and functional flexibility. This approach is based on Amphibious logic combining a high-level design LSI-CAD system with a functionally reconfigurable Field Programmable Gate Array (FPGA). Functions are programmed via a behavioral description program in a high-level design LSI-CAD system. In order to show the effectiveness of the newly proposed Amphibious logic approach, we designed JPEG-type Huffman and arithmetic CODECs for encoding still images. A comparison with the results of the processing speeds of DSPs and general-purpose microprocessors proves that the Amphibious logic is indeed possible to attain the dual goals of high performance and programmability. The proposed approach can be used to augment a conventional DSP by allocating the functions of numerical processing and bit stream processing, as used in image coding algorithms, between DSPs and FPGAs.

Similar content being viewed by others

References

R. C. Gonzalez and P. Wintz. Digital Image Processing. Addison-Wesley, second edition, 1987.

S.-M. Lei and M.-T. Sun. An entropy coding system for digital HDTV applications. IEEE Trans. Circuits Syst. Video Technol, 1(1):147–155, March 1991.

S.-F. Chang and D. G. Messerschumitt. Designing a high-throughput VLC decoder. Part I—Concurrent VLSI architectures. IEEE Trans. Circuits and Syst. for Video Technol., 2(2): 187–196, June 1992.

H.-D. Lin and D. G. Messerschumitt. Designing a high-throughput VLC decoderr. Part II—Parallel decoding methods. IEEE Trans. Circuits and Syst. for Video Technol., 2(2): 197–206, June 1992.

(JPEG) ISO CD 10918. Digital Compression and Coding of Continuous-Tone Still Images. ISO/IEC JTC1/SC2/WG10, January 1991.

I. Furukawa, K. Kashiwabuchi, and S. Ono. Super high definition image digitizing system. In Proc. Int. Conf. Acoust. Speech, Signal Processing '92, pages III-529-532, March 1992.

R. C. Fairfield, A. Matusevich, and J. Plany. An LSI digital encryption processor (DEP). IEEE Communications Magazine, 23(7):30–41, July 1985.

CCITT. Recommendation G.721 - 32 kbit/sec adaptive differential pulse code modulation (ADPCM). Red Book, vol. III, Fascicle III.3, pp.125–160, October 1984.

A. Haines. Field programmable gate array with non-volatile configuration. Microprocessors and Microsystems, 13(5):305–312, June 1989.

DAS of IEEE, IEEE Standard VHDL Language Reference Manual, IEEE Std.1076, 1987.

Y. Nakamura. An integrated logic design environment based on behavioral description. IEEE Trans. Computer-Aided Design, CAD-6(3):322–336, May 1987.

Y. Nakamura, K. Oguri, A. Nagoya, and R. Nomura. A hierarchical behavioral description based CAD system. In Proc. EURO ASIC'90, pages 282–287, May 1990.

A. Nagoya, Y. Nakamura, K. Oguri, and R. Nomura. Multi-level logic optimization for large scale ASICs'. In Proc. Int. Conf. Computer-Aided Design'90, pages 564–567, November 1990.

T. Sawabe, T. Fujii, H. Nakada, N. Ohta, and S. Ono. A 15 GFLOPS parallel DSP system for super high definition image processing. Trans. IEICE of Japan, E75-A(7):786–793, July 1992.

INMOS Limited. Transputer Technical Notes. Prentice Hall, 1989.

Sun Microsystems, Inc. Spare Architecture Manual. Mountain View, CA, 1987.

Mips Computer Systems, Inc. MIPS R4000 Microprocessor User's Manual. Sunnyvale, CA, 1991.

Xilinx, Inc. Programmable Gate Array Data Book. 1991.

Y. Komagata and T. Noda. MB86356 color still image compression and decompression LSI. FUJITSU, 43(2):117–122, February 1992.

Kubota C-Cube, Inc. CL550 JPEG Image Compression Processor Data Book. 1992.

C. Loeffler, A. Ligtenberg, and G. S. Moschytz. Practical fast 1-D DCT algorithms with 11 multiplications. In Proc. Int. Conf. Acoust. Speech. Signal Processing'89, pages 988–991, May 1989.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Suzuki, J., Ono, S. Entropy CODEC from behavioral description based LSI-CAD for fully programmable image coding system. Des Autom Embed Syst 1, 231–255 (1996). https://doi.org/10.1007/BF00133304

Issue Date:

DOI: https://doi.org/10.1007/BF00133304