Abstract

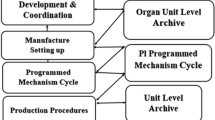

Even high stuck-at fault coverage manufacturing test programs cannot assure high quality for CMOS VLSI circuits. Measurement of quiescent power supply current (I DDQ ) is a means of improving quality and reliability by detecting many defects that do not have appropriate representation in the stuck-at fault model. Since each I DDQ measurement takes significant time, a hierarchical fault analysis methodology is proposed for selecting a small subset of production test vectors for I DDQ measurements. A software system QUIETEST has been developed on the basis of this methodology. For two VLSI circuits QUIETEST selected less than 1% of production test vectors for covering all modeled faults that would have been covered by I DDQ measurement for all of the vectors. The fault models include leakage faults and weak faults for representing defects such as gate oxide shorts and certain opens.

Similar content being viewed by others

References

S. McEuen, “I DDQ benefits,” Proc. VLSI Test Symp., pp. 285–291, 1991.

C.F. Hawkins and J.M. Soden, “Electrical characteristics and testing considerations for gate oxide shorts in CMOS ICs,” Proc. Int. Test Conf., pp. 544–555, 1985.

J.M. Soden, R.K. Treece, M.R. Taylor and C.F. Hawkins, “CMOS IC stuck-open fault electrical effects and design considerations,” Proc. Int. Test Conf., pp. 423–430, 1989.

J.M. Soden and C.F. Hawkins, “Test considerations for gate oxide shorts in CMOS ICs,” IEEE Design & Test of Comp., vol. 3, pp. 56–64, August 1986.

C.F. Hawkins and J.M. Soden, “Reliability and electrical properties of gate oxide shorts in CMOS ICs,” Proc. Int. Test Conf., pp. 443–451, 1986.

J.M. Soden and C.F. Hawkins, “Electrical properties and detection methods for CMOS IC defects,” Proc. 1st European Test Conf., pp. 159–167, 1989.

F.J. Ferguson, M. Taylor and T. Larrabee, “Testing for parametric faults in static CMOS circuits,” Proc. Int. Test Conf., pp. 436–443, 1990.

Y.K. Malaiya and S.Y.H. Su, “A new fault model and testing technique for CMOS devices,” Proc. Int. Test Conf., pp. 25–34, 1982.

W. Maly and P. Nigh, “Built-in current testing: Feasibility study,” Proc. Int. Conf. on Computer-Aided Design, pp. 340–343, 1988.

L.K. Horning, J.M. Soden, R.R. Fritzemeier and C.F. Hawkins, “Measurements of quiescent power supply current for CMOS ICs in production testing,” Proc. Int. Test Conf., pp. 300–308, 1987.

C. Crapuchettes, “Testing CMOS I DD on large devices,” Proc. Int. Test Conf., pp. 310–315, 1987.

M. Keating and D. Meyer, “A new approach to dynamic I DD testing,” Proc. Int. Test Conf., pp. 316–321, 1987.

W. Mao, R.K. Gulati, D.K. Goel and M.D. Ciletti, “QUIETEST: A quiescent current testing methodology for detecting leakage faults,” Proc. Int. Conf. on Computer-Aided Design, pp. 280–283, 1990.

R.K. Gulati, W. Mao and D.K. Goel, “Detection of undetectable faults using I DDQ testing,” Proc. Int. Test Conf., pp. 770–777, 1992.

N. Weste and K. Eshraghian, “Principles of CMOS VLSI design,” Reading, MA: Addison-Wesley, 1985.

Special issue on “Switch level techniques,” IEEE Design and Test of Comp., vol. 4, August 1987.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Mao, W., Gulati, R.K. Quietest: A methodology for selecting I DDQ test vectors. J Electron Test 3, 349–357 (1992). https://doi.org/10.1007/BF00135338

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF00135338