Abstract

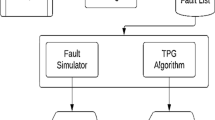

Automatic test pattern generation (ATPG) for sequential circuits involves making decisions in the search decision spaces bounded by a sequential circuit. The flip-flops in the sequential circuit determine the circuit state search decision space. The inputs of the circuit define the combinational search decision space. Much work on sequential circuit ATPG acceleration focused on how to make ATPG search decisions. We propose a new technique to improve sequential circuit ATPG efficiency by focusing on not repeating previous searches. This new method is orthogonal to existing deterministic sequential circuit ATPG algorithms.

A common search operation in sequential circuit ATPG is justification, which is to find an input assignment to justify a desired output assignment of a component. We have observed that implications in a circuit resulting from prior justification decisions form an unique justification decomposition. Since the connectivity of a circuit does not change during ATPG, test generation for different target faults may share identical justification decision sequences represented by identical decision spaces. Because justification decomposition represents the collective effects of prior justification decisions, it is used to identify previously-explored justification decisions. Preliminary results on the ISCAS 1989 circuits show that our test generator (SEST) using justification decompositions, on average, runs 2.4 and 4.5 times faster than Gentest and Hitec, respectively. We describe the details of justification equivalence and its application in ATPG accompanied with step-by-step examples.

Similar content being viewed by others

References

V.K. Agrawal and A.S.F. Fung, “Multiple Fault Testing of Large Circuits by Single Fault Test Sets,” IEEE Transactions on Computers, Vol. 30, pp. 855–865, November 1981.

J.L.A. Hughes and E.J. McCluskey, “Multiple Stuck-at Fault Coverage of Single Fault Test Sets,” in Proceedings of International Test Conference, September 1986, pp. 368–374.

J. Jacob and N.N. Biswas, “GTBD Faults and Lower Bounds on Multiple Fault Coverage of Single Fault Test Sets,” in Proceedings of International Test Conference, September 1987, pp. 849–855.

R.A. Marlett, “EBT: A Comprehensive Test Generation Technique for Highly Sequential Circuits,” in Proceedings of the 15th Design Automation Conference, June 1978, pp. 335–339.

R.A. Marlett, “An Efficient Test Generation System for Sequential Circuits,” in Proceedings of the 23rd Design Automation Conference, June 1986, pp. 250–256.

O.H. Ibarra and S.K. Sahni, “Polynomially Complete Fault Detection Problems,” IEEE Transactions on Computers, Vol. 24, pp. 242–249, March 1975.

M. Abramovici, M.A. Breuer, and A.D. Friedman, Digital Systems Testing and Testable Design, New York: Computer Science Press, W.H. Freeman and Company, 1990.

W.T. Cheng, “The BACK Algorithm for Sequential Test Generation,” in Proceedings of the International Conference on Computer Design, August 1988, pp. 66–69.

W.T. Cheng, “SPLIT Circuit Model for Test Generation,” in Proceedings of the 25th Design Automation Conference, June 1988, pp. 96–101.

W.T. Cheng and T.J. Chakraborty, “GENTEST: An Automatic Test Generation System for Sequential Circuits,” IEEE Computer, Vol. 38, pp. 43–49, April 1989.

H.K.T. Ma, S. Devadas, A.R. Newton, and A. Sangiovanni-Vincentelli, “Test Generation for Sequential Circuits,” IEEE Transactions on Computer-Aided Design, Vol. 7, pp. 1081–1093, October 1988.

A. Ghosh, S. Devadas, and A.R. Newton, “Test Generation for Highly Sequential Circuits,” in Proceedings of the International Conference on Computer Design, November 1989, pp. 362–365.

T.M. Niermann and J.H. Patel, “HITEC: A Test Generation Package for Sequential Circuits,” in Proceedings of the European Conference on Design Automation, February 1991, pp. 214–218.

P. Goel, “An Implicit Enumeration Algorithm to Generate Tests for Combinational Logic Circuits,” IEEE Transactions on Computers, Vol. 30, pp. 215–222, March 1981.

H. Fujiwara and T. Shimono, “On the Acceleration of Test Generation Algorithms,” in Digest of Papers of the 13rd Fault-Tolerant Computing Symposium, August 1983, pp. 98–105.

T. Kirkland and M.R. Mercer, “A Topological Search Algorithm for ATPG,” in Proceedings of the 24th Design Automation Conference, June 1987, pp. 502–508.

M.H. Schulz, E. Trischler, and T.M. Sarfert, “SOCRATES: A Highly Efficient Automatic Test Pattern Generation System,” in Proceedings of International Test Conference, September 1987, pp. 1016–1026.

E. Auth and M.H. Schulz, “A Test-Pattern-Generation Algorithm for Sequential Circuits,” IEEE Design & Test of Computers, Vol. 8, pp. 72–86, June 1991.

T.P. Kelsey, K.K. Saluja, and S.Y. Lee, “An Efficient Algorithm for Sequential Circuit Test Generation,” IEEE Transactions on Computers, Vol. 42, pp. 1361–1371, November 1993.

N. Gouders and R. Kaibel, “Advanced Techniques for Sequential Test Generation,” in Proceedings of the 2nd European Test Conference, April 1991, pp. 293–300.

J. Rajski and H. Cox, “A Method to Calculate Necessary Assignments in Algorithmic Test Pattern Generation,” in Proceedings of International Test Conference, August 1990, pp. 25–34.

H. Cho, G.D. Hachtel, E. Macii, M. Poncino, and F. Somenzi, “A State Space Decomposition Algorithm for Approximate FSM Traversal,” in Proceedings of the European Design and Test Conference, February 1994, pp. 137–141.

H. Cho, G.D. Hachtel, and F. Somenzi, “Redundancy Identification/Removal and Test Generation for Sequential Circuits Using Implicit State Enumeration,” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol. 12, pp. 935–945, July 1993.

H. Cho, S. Jeong, F. Somenzi, and C. Pixley, “Synchronizing Sequences and Symbolic Traversal Techniques in Test Generation,” Journal of Electronic Testing: Theory and Applications, Vol. 4, pp. 19–31, February 1993.

I. Pomeranz and S.M. Reddy, “The Multiple Observation Time Test Strategy,” IEEE Transactions on Computers, Vol. 41, pp. 627–637, May 1992.

I. Pomeranz and S.M. Reddy, “Application of Homing Sequences to Synchronous Sequential Circuit Testing,” in Proceedings of the Second Asian Test Symposium, November 1993, pp. 324–329.

V.D. Agrawal, K.T. Cheng, and P. Agrawal, “CONTEST: A Concurrent Test Generator for Sequential Circuits,” in Proceedings of the 25th Design Automation Conference, June 1988, pp. 84–89.

K.T. Cheng and V.D. Agrawal, “A Sequential Circuit Test Generator Using Threshold-Value Simulation,” in Digest of Papers of the 18th Fault-Tolerant Computing Symposium, August 1988, pp. 24–29.

K. Hatayama, M.I.K. Hikone, and T. Hayashi, “Sequential Test Generation Based on Real-Valued Logic Simulation,” in Proceedings of International Test Conference, September 1992, pp. 41–48.

V.D. Agrawal and S.C. Seth, Tutorial—Test Generation for VLSI Chips, Washington, D.C.: IEEE Computer Society Press, 1988.

V.D. Agrawal, C.R. Kime, and K.K. Saluja, “A Tutorial on Built-In Self-Test, Part 1: Principles,” IEEE Design & Test of Computers, Vol. 10, pp. 73–82, March 1993.

V.D. Agrawal, C.R. Kime, and K.K. Saluja, “A Tutorial on Built-In Self-Test, Part 2: Applications,” IEEE Design & Test of Computers, Vol. 10, pp. 69–77, June 1993.

V.D. Agrawal and S.T. Chakradhar, “Combinational ATPG Theorems for Identifying Untestable Faults in Sequential Circuits,” IEEE Transactions on Computer-Aided Design, Vol. 14, pp. 1155–1160, September 1995.

J. Giraldi and M.L. Bushnell, “EST: The New Frontier in Automatic Test Pattern Generation,” in Proceedings of the 27th Design Automation Conference, June 1990, pp. 667–672.

R.S. Wei and A. Sangiovanni-Vincentelli, “PLATYPUS: A PLA Test Generation Tool,” IEEE Transactions on Computer-Aided Design, Vol. 5, pp. 633–634, June 1986.

R.S. Wei and A. Sangiovanni-Vincentelli, “PROTEUS: A Logic Verification System for Combinational Circuits,” in Proceedings of International Test Conference, September 1986, pp. 350–359.

X. Chen and M.L. Bushnell, “Generalization of Search State Equivalence for Automatic Test Pattern Generation,” in Proceedings of the 8th International Conference on VLSI Design, January 1995, pp. 99–103.

X. Chen and M.L. Bushnell, “Dynamic State and Objective Learning for Sequential Circuit Automatic Test Generation Using Decomposition Equivalence,” in Digest of Papers of the 24th Fault-Tolerant Computing Symposium, June 1994, pp. 446–455.

F. Brglez, D. Bryan, and K. Kozminski, “Combinational Profiles of Sequential Benchmark Circuits,” in Proceedings of International Symposium on Circuits and Systems, June 1989, pp. 1929–1934.

K.T. Cheng and H.K.T. Ma, “On the Over-Specification Problem in Sequential ATPG Algorithms,” in Proceedings of the 29th Design Automation Conference, June 1992, pp. 16–21.

P. Muth, “A Nine-Valued Circuit Model for Test Generation,” IEEE Transactions on Computers, Vol. 25, pp. 630–636, June 1976.

M.A. Iyer and M. Abramovici, “Low-Cost Redundancy Identification for Combinational Circuits,” in Proceedings of the 7th International Conference on VLSI Design, January 1994, pp. 315–318.

L.H. Goldstein and E.L. Thigpen, “SCOAP: Sandia Controllability/Observability Analysis Program,” in Proceedings of the 17th Design Automation Conference, June 1980, pp. 190–196.

W.T. Cheng and S. Davidson, “Sequential Circuit Test Generator STG Benchmark Results,” in Proceedings of International Symposium on Circuits and Systems, June 1989, pp. 1939–1941.

J.H. Patel, T.M. Niermann, J. Lee, and L. Rudnick, “High Level Test Generation,” in Semiconductor Research Corporation Review of the Program in Reliable VLSI Architectures, University of Illinois at Urbana-Champaign, May 1991.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Chen, X., Bushnell, M.L. Sequential circuit test generation using dynamic justification equivalence. J Electron Test 8, 9–33 (1996). https://doi.org/10.1007/BF00136073

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF00136073