Abstract

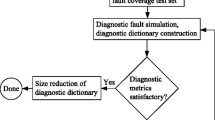

Two faults are said to be equivalent, with respect to a test set τ, iff they cannot be distinguished by any test in τ. The sizes of the corresponding equivalence classes of faults are used as a basis for comparing the diagnostic capability of two given test sets. A novel algorithm, called “multiway list splitting,” for computing the Equivalence Classes of stuck-at faults, in combinational (full scan) circuits, with respect to a given test set is presented. Experimental results presented show the algorithm to be more efficient than previously known algorithms based on decision diagrams and diagnosibility matrix.

Similar content being viewed by others

References

M. Abramovici, M.A. Breuer, and A.D. Friedman, Digital Systems Testing and Testable Design, Computer Science Press, 1990.

P. Camurati, D. Medine, P. Prinetto, and M.S. Reorda, “A Diagnostic Test Pattern Generation Algorithm,” Proceedings of the International Test Conference, 1990, pp. 52–58.

T. Grüning, H. Koopmeiners, and U. Mahlstedt, “DIAGTEST: A Fast Diagnostic Test Pattern Generator for Combinational Circuits,” Digest of Papers, International Conference on Computer-Aided Design, pp. 194–197, 1991.

K. Kubiak, S. Parkes, W.K. Fuchs, and R. Saleh, “Exact Evaluation of Diagnostic Test Resolution,” Proc. 29th Design Automation Conf., June 1992, pp. 347–352.

Elizabeth M. Rudnick, W. Kent Fuchs, and Janak H. Patel, “Diagnostic Fault Simulation of Sequential Circuits,” Proceedings of the International Test Conference, 1992, pp. 178–186.

T.M. Niermann, W.-T. Cheng, and J.H. Patel, “PROOFS: A Fast, Memory-Efficient Sequential Circuit Fault Simulator,” IEEE Trans. CAD, pp. 198–207, February 1992.

E.M. Rudnick, T.M. Niermann, and J.H. Patel, “Methods for Reducing Events in Sequential Circuit Fault Simulation,” Proc. International Conference on Computer-Aided Design, 1991, pp. 546–549.

John A. Waicukauski, Ved P. Gupta, and Sanjay T. Patel, “Diagnosis of BIST failures by PPSFP Simulation,” 1987 International Test Conference, pp. 480–484.

G. Ryan, W.K. Fuchs, and I. Pomeranz, “Fault Dictionary Compression and Equivalence Class Computation for Sequential Circuits,” Proc. International Conference on Computer-Aided Design, 1993, pp. 508–511.

Thomas H. Cormen, Charles E. Leiserson, and Ronald L. Rivest, Introduction to Algorithms, McGraw-Hill, Second printing 1990.

F. Maamari and J. Rajski, “A Method of Fault Simulation Based on Stem Regions,” IEEE Trans. on CAD, Vol. CAD-9(2), pp. 212–220, February 1990.

S. Chakravarty and Y. Gong, “An Algorithm for Diagnosing Two-Line Bridging Faults in Combinational Circuits,” Tech. Report 92-26, Dept. of Computer Science, SUNY at Buffalo.

T.M. Niermann, W.-T. Cheng, and J.H. Patel, “PROOFS: A Fast, Memory-Efficient Sequential Circuit Fault Simulator,” IEEE Trans. on Computer Aided Design, pp. 198–207, February 1992.

Hyung K. Lee and Dong S. Ha, “Comments on ‘A Method of Fault Simulation Based on Stem Regions’,” IEEE Trans. on CAD, Vol. 11(3), pp. 407–408.

D. Harel and B. Krishnamurthy, “Is There Hope for Linear Time Fault Simulation?” Proc. 17th Fault Tolerant Computing Symp., 1987, pp. 28–33.

F. Brglez and H. Fujiwara, “A Neutral Netlist of 10 Combinational Benchmark Circuits and a Target Translator in FOR-TRAN,” Special Session on ATPG and Fault Simulation, International Symposium on Circuits and Systems, 1985.

S. Chakravarty and Y. Gong, “Diagnostic Simulation of Stuck-at Faults in Combinational Circuits,” 12th IEEE VLSI Test Symposium, pp. 128–133, 1993.

Author information

Authors and Affiliations

Additional information

Portions of this work were presented in [1].

Research Supported by NFS Grant No. MIP9102509.

Research Supported by SRC Grant 93-DP-109.

Rights and permissions

About this article

Cite this article

Chakravarty, S., Gong, Y. & Venkataraman, S. Diagnostic simulation of stuck-at faults in combinational circuits. J Electron Test 8, 87–97 (1996). https://doi.org/10.1007/BF00136078

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF00136078