Abstract

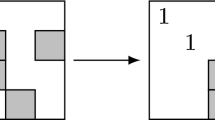

This paper presents an efficient automatic test pattern generation technique for loop-free circuits. A partial scan technique is used to convert a sequential circuit (finite state machine) with arbitrary feedback paths into a pipelined circuit for testing. Test generation for these modified circuits can be performed with a modified combinational automatic test pattern generator (ATPG), which is much faster than a sequential ATPG. A combinational model is obtained by replacing all flipflops by buffers. It is shown that a test vector for a fault in this model obtained by a combinational test generator can be expanded into a sequence of identical vectors to detect the same fault in the original sequential circuit. This technique may abort a few faults which can then be resolved with a sequential ATPG. Experiments on the ISCAS89 circuits show that only 30% to 70% of flipflops require scanning in larger circuits and 96% to 100% fault coverage for almost all the circuits without resorting to a sequential ATPG.

Similar content being viewed by others

References

R.A. Marlett, “EBT: A comprehensive test generation technique for highly sequential circuits,” Proceedings of the 15th Design Automation Conference, pp. 335–339, June 1978.

R.A. Marlett, “An effective test generation system for sequential circuits,” Proceedings of the 23rd Design Automation Conference, pp. 250–256, June 1986.

H.K.T. Ma, S. Devadas, A.R. Newton, and A. SangiovanniVincentelli, “Test generation for sequential finite state machines,” Proceedings of the International Conference on Computer Aided Design, pp. 288–291, Nov. 1987.

W.T. Cheng, “The back algorithm for sequential test generation,” Proceedings of the International Conference on Computer Design, pp. 66–69, October 1988.

M.H. Schulz, and E. Auth, “ESSENTIAL: An efficient selflearning test pattern generation algorithm for sequential circuits,” Proceedings of the International Test Conference, pp. 28–37, August 1989.

E.B. Eichelberger, and T.W. Williams, “A logic design structure of LSI testing,” Proceedings of the 14th Design Automation Conference, pp. 462–468, June 1977.

E. Trischler, “Testability Analysis and Incomplete Scan Path,” Proceedings of International Conference on Computer Aided Design, pp. 38–39, Oct. 1983.

V.D. Agrawal, K.T. Cheng, D.D. Johnson, and T. Lin, “A complete solution to the partial scan problem,” Proceedings of the International Test Conference, pp. 44–51, 1987.

K.T. Cheng, and V.D. Agrawal, “A partial scan method for sequential circuits with feedback,” IEEE Transactions on Computers, vol. C-39, pp. 544–548, April 1990.

S. Lee, and K.G. Shin, “Design for test using partial parallel scan,” IEEE Transactions on Computer-Aided design, vol. CAD-9, pp. 203–211, February 1990.

R. Gupta, R. Gupta, and M.A. Breuer, “The BALLAST methodology for structured partial scan design,” IEEE Transactions on Computers, vol. C-39, pp. 538–544, April 1990.

A. Miczo, Digital Logic Testing and Simulation, New York: Harper & Row, pp. 98–103, 1986.

F. Brglez, D. Bryan, and C. Kozminski, “Combinational profiles of sequential benchmark circuits,” special session on benchmarks for sequential test pattern generation, Proceedings of the International Symposium on Circuits and Systems, 1989.

P. Goel, “An implicit enumeration algorithm to generate tests for combinational logic circuits,” IEEE Transactions on Computers, vol. C-30, pp. 215–222, March 1981.

H. Fujiwara, and T. Shimono, “On the acceleration of test generation algorithms,” IEEE Transactions on Computers, vol. C-32, pp. 1137–1144, December 1983.

M.H. Schulz, E. Trischler, and T.M. Sarfert, “SOCRATES: A highly efficient automatic test pattern generation system,” IEEE Transactions on Computer-Aided Design, vol. CAD-7, pp. 126–137, January 1988.

K.T. Cheng, and V.D. Agrawal, “An economical scan design for sequential logic test generation,” Proceedings of the 19th Symposium on Fault Tolerant Computing, pp. 28–35, June 1989.

E. Horowitz, and S. Sahni, Fundamentals of Computer Algorithms, Potomac, MD: Computer Science Press, p. 193, 1978.

P. Goel, “Test generation costs analysis and projections,” Proceedings of the 17th ACM/IEEE Design Automation Conference, pp. 77–84, June 1980.

H.B. Min, and W.A. Rogers, “Search strategy switching: An alternative to increased backtracking,” Proceedings of the International Test Conference, pp. 803–811, August 1989.

R. Tarjan, “Finding dominators in directed graph,” SIAM Journal on Computing, vol. 3, pp. 62–89, 1974.

D.B. Johnson, “Finding all the elementary circuits of a directed graph,” SIAM Journal on Computing, vol. 4, (1), pp. 77–84, 1975.

Author information

Authors and Affiliations

Additional information

This research was sponsored by the Semiconductor Research Corporation, Contract 90-DP-142.

Rights and permissions

About this article

Cite this article

Min, H.B., Rogers, W.A. A test methodology for finite state machines using partial scan design. J Electron Test 3, 127–137 (1992). https://doi.org/10.1007/BF00137250

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF00137250