Abstract

In this paper we have investigated a unified and simultaneous fault detection method for mixed-signal integrated circuits. The method is based on the analysis of the power-supply current through the circuit under test. The analysis has been done paying attention to the dynamic behaviour of the power-supply current, in order to avoid measurement problems related to the large amount of quiescent current drop across many analog blocks.

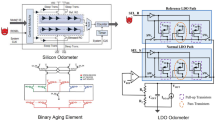

The analysis of the dynamic power-supply current entails certain problems related to the complexity of the measurement process, especially those due to the high speed of the current transients. These problems have been addressed by considering a design for test procedure based on the use of built-in dynamic current sensors.

The goal of the design for test methodology proposed is to represent the Iddt through the mixed-signal IC under test by a digital signature. The paper presents some advantages of this approach such as a good tolerance to cross-talk noise and the need for only a conventional digital tester on the complete mixed-signal IC for fault detection. The analysis is illustrated with some test results.

Similar content being viewed by others

References

W. Hochwald and J. Bastian, “A DC Approach for Analog Fault Dictionary Determination,” IEEE Trans. on Circuits and Systems, Vol. CAS-26, No. 7, pp. 523–529, July 1979.

M. Al-Qutayri and P.R. Shepherd, “On the Testing of Mixed-Mode Integrated Circuits,” Journal of Semicustom ICs, Vol. 7, No. 4, pp. 32–39, June 1990.

D. Brown and J. Damianos, “Method for Simulation and Testing of Analogue-Digital Circuits,” IBM Tech. Disclosure Bulletin., Vol. 25, pp. 6367–6368, 1983.

P.S.A. Evans, M. Al-Qutayri, and P.R. Sheperd, “On the Development of Transient Response Testing Techniques for Mixed-Mode ICs,” Journal of Semicustom ICs, Vol. 8, No. 2, pp. 34–39, Dec. 1990.

K.R. Eckersall, PL. Wrighton, I.M. Bell, B.R. Bannister, and G.E. Taylor, “Testing Mixed-Signal ASICs Through the Use of Supply Current Monitoring,” Proceedings of the European Test Conference, 1993, pp. 385–391.

A.H. Bratt, R.J. Harvey, A.P. Dorey, and A.M. Richardson, “Aspects of Current Reference Generation and Distribution for I ddx Pass/Fail Current Threshold Determination,” IEE Colloquium on Mixed Signal VLSI Test, Dec. 1993, pp. 3/1–3/7.

P. O'Leary and P. Lee, “Fault Detection Method Using Power Supply Spectrum Analysis,” Electronics Letters, Vol. 26, No. 20, pp. 1733–1734, Sept. 27 1990.

I.M. Bell, D.A. Camplin, G.E. Taylor, and B.R. Bannister, “Supply Current Testing of Mixed Analogue and Digital Integrated Circuits,” Electronics Letters, Vol. 27, No. 17, pp. 1581–1583, 15th Aug. 1991.

M. Al-Qutayri and P.R. Sheperd, “Go/No-Go Testing of Analogue Macros,” IEE Proceedings-G, Vol. 139, No. 4. Aug. 1992, pp. 534–540.

S. Bracho, M. Martínez, and J. Argüelles, “Test Generation and Fault Detection Techniques in Mixed Circuits,” 35th Midwest Symposium on Circuits and Systems, Washington, DC, Aug. 1992, pp. 931–937.

M. Keating and D. Meyer, “A New Approach to Dynamic I dd Testing,” Proceedings of the International Test Conference, 1987, pp. 316–321.

A.P. Dorey, B.K. Jones, A.M. Richardson, P.C. Russel, and Y.Z. Xu, “Reliability Testing by Precise Electrical Measurement,” Proceedings of the International Test Conference, 1988, pp. 369–373.

G.E. Taylor, I.M. Bell, P. Miller, and J. Compton, “Testing of Mixed Signal (Analogue and Digital) Circuits (Asic and Board Level) Using Current Monitoring Techniques,” IEE Colloquium on Mixed Signal VLSI Test, Dec. 1993, pp. 4/1–4/6.

J.F. Frenzel and P.N. Marinos, “Power Supply Current Signature (PSCS) Analysis: A New Approach to System Testing,” Proceedings of the International Test Conference, 1987, pp. 125–135.

Z. Wang, G. Gielen, and W. Sansen, “Testing of Analogue IC Based on Power-Supply Current Monitoring and Discrimination Analysis,” Third Asian Test Symposium, Nov. 1994, pp. 126–131.

J. Argüelles, M. Martínez, and S. Bracho, “Dynamic I DD Test Circuitry for Mixed Signal ICs,” Electronics Letters, Vol. 30, No. 6, pp. 485–486, March 17 1994.

P. Banerjee and J.A. Abraham, “Fault Characterization of VLSI MOS Circuits,” Proceedings of the IEEE International Conference on Circuits and Computers, 1982, pp. 564–568.

D.K. Su, M.J. Loinaz, S. Mausi, and B.A. Wooley, “Experimental Results and Modeling techniques for Substrate Noise in Mixed-Signal Integrated Circuits,” IEEE Journal of Solid-State Circuits, Vol. 28, No. 4, pp. 420–430, April 1993.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Argüelles, J., Bracho, S. Signature analysis for fault detection of mixed-signal ICs based on dynamic power-supply current. J Electron Test 9, 89–107 (1996). https://doi.org/10.1007/BF00137567

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF00137567