Abstract

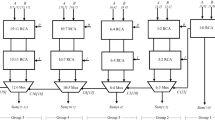

Carry-save arithmetic, well known from multiplier architectures, can be used for the efficient CMOS implementation of a much wider variety of algorithms for high-speed digital signal processing than, only multiplication. Existing architectural strategies and circuit concepts for the realization of inner-product based and recursive algorithms are recalled. The two's complement overflow behavior of carry-save arithmetic is analyzed and efficient overflow correction schemes are given. Efficient approaches are presented for the carry-save, implementation of a saturation control. The concepts are extended and refined for the high-throughput implementation of decisiondirected algorithms such as division, modulo multiplication and CORDIC which have yet been avoided because of a lack of efficient concepts for implementation.

It is shown, that the carry-save technique can be extended to a comprehensive method to implement high-speed DSP algorithms. Successfully fabricated commercial VLSI circuits emphasize the potential of this method.

Similar content being viewed by others

References

A. Avizienis, “Signed-Digit Number Representations for Fast Parallel Arithmetic”,IRE Trans. on Electronic Computers, 1961, pp. 389–400,

B. Parhami, “Generalized Signed-Digit Number Systems: A Unifying Framework for Redundant Number Representations”,IEEE Trans. on Computers, vol. 39, 1990, pp. 89–98.

J.V. McCanny and J.G. McWhirter, “Completely Iterative, Pipelined Multiplier Array Suitable for VLSI”,IEE Proc. Pt. G, vol. 129, 1982, pp. 40–46.

P.R. Cappello and K. Steiglitz, “A Note on ‘Free Accumulation’ in VLSI Filter Architectures”,IEEE Trans. on Circuits and Systems, vol. CAS-32, 1985, pp. 291–296.

T.G. Noll et al. “A Pipelined 330-MHz Multiplier”,IEEE Journal of Solid-State Circuits, vol. SC-21, 1986, pp. 411–416.

M. Hatamian and G.L. Cash, “Parallel Bit-Level Pipelined VLSI Designs for High-Speed Signal Processing”,Proc. of the IEEE, vol. 75, 1987, pp. 1192–1202.

T.G. Noll, “Architektur-und Schaltungsentwurf eines digitalen adaptiven Entzerrers für den Digital-Richtfunk mit lokal systolischen Carry-Save-Arrays in CMOS-Technologie”, Doctoral Dissertation, Ruhr-University Bochum, 1989.

T.G. Noll “Semi-Systolic Maximum Rate Transversal Filters with Programmable Coefficients”, inSystolic Arrays, (W. Moore et al., Eds.), Bristol: Adam Hilger, 1987.

U. Kleine and M. Böhner, “A High-Speed Wave Digital Filter Using Carry-Save Arithmetic”,Proc. of ESSCIRC ′87, Bad Soden 1987, pp. 43–46.

W. Kamp, K. Knauer, and E. Lackerschmid, “A Fast 16×16 Bit Asynchronous CMOS Multiplier”Proc. of ESSCIRC ′86, Delft 1986, pp. A4.4–A4.6.

S.C. Knowles et al., “Bit-Level Systolic Architectures for High Performance IIR Filtering”,Journal of VLSI Signal Processing, vol. 1, 1989, pp. 9–24.

W. Ulbrich, A. Reiner, and T.G. Noll, “Digitales Rechenwerk”, European Patent No. 0 130 397/B1.

U. Totzek et al., “CMOS VLSI Implementation of the 2D-DCT with Linear Processor Arrays”,Proc. of ICASSP ′90, Albuquerque April 1990, pp. 937–940.

T.G. Noll and U. Kleine, Patent pending.

U. Kleine and T.G. Noll, “On the Forced Response Stability of Wave Digital Filters Using Carry-Save Arithmetic”, AEÜ Bd. 41, 1987, pp. 321–324.

U. Kleine and T.G. Noll, “Wave Digital Filters Using Carry-Save Arithmetic”,ISCAS ′88, Espoo 1988, pp. 1757–1762.

P.B. Denyer and D.J. Myers, “Carry-Save Arrays for VLSI Processing”,Proc. of First Int. Conf. on VLSI, Edinburgh, 1981, pp. 151–160.

S.R. Meier et al., “A 2 μm CMOS Digital Adaptive Equalizer Chip for QAM Digital Radio Modems”,IEEE Journal of Solid-State Circuits, vol. SC-23, 1988, pp. 1212–1217.

W. Haberecht, E. DeMan, and M. Schulz: “A Programmable 32 Tap Digital Interpolation Filter in 1.5 μm CMOS with 80 MHz Output Data Rate”,Proc. of CICC ′90, Boston, 1990, pp. S13.1.

E. DeMan, M. Schulz, and W. Haberecht, “A Digital Interpolation Filter Chip with 32 Programmable Coefficients for 80 MHz Sampling Frequency”,IEEE Journal of Solid-State Circuits, forthcoming, 1991.

W. Kamp et al., “Programmable 2D Linear Filter for Video Applications”,IEEE Journal of Solid-State Circuits, vol. SC-25, 1990, pp. 735–740.

S.R. Meier, R. Künemund, and T.G. Noll, Patent pending.

W. Ulbrich and T.G. Noll, “Design of Dedicated MOS Digital Filters for High-Speed Applications”,Proc. of ISCAS ′85, Kyoto 1985, pp. 255–258.

T.G. Noll and W. Ulbrich, “Semi-Systolic Arrays for High-Speed Digital Filters in VLSI-MOS”,Proc. of IASTED ′85, Paris 1985, pp. 160–258.

W. Lao and H. Samueli, “Architecture and Design of a High-Speed CMOS 15th Order Half-Band Recursive Digital Filter”,Proc. of Midwest Symp. on Circuit and Systems, St. Louis, 1988.

H.H. Loomis, “The Maximum Rate Accumulator”,IEEE Trans. on Electronic Computers vol. EC-15, 1966, pp. 628–639.

K.K. Parhi and D.G. Messerschmitt “Pipeline Interleaving and Parallelism in Recursive Digital Filters—Part I”,IEEE Trans. on Acoustics, Speech and Signal Processing, vol. 37, 1989, pp. 1099–1117.

G. Fettweis and H. Meyr, “A Systolic Array Viterbi Processor for High Data Rates”,Int. Conf. on Systolic Arrays, Ireland, 1989,Systolic Array Processors, Englewood Cliffs, NJ: Prentice Hall, 1989.

G. Sebald, B. Lankl, and J.A. Nossek, “Advanced Time- and Frequency-Domain Adaptive Equalization in Multilevel QAM Digital Radio Systems”,IEEE Journal on Selected Areas in Communications, vol. SAC-5 (3), 1987, pp. 448–456.

M. Schöbinger, J. Härtl, and T.G. Noll, “CMOS Digital Adaptive Decision Feedback Equalizer Chip for Multilevel QAM Digital Radio Modems”,Proc. of ISCAS ′90, New Orleans, 1990, pp. 574–577.

K. Hwang,Computer Arithmetic, New York: John Wiley, 1979.

H.Y. Lo, “An Improvement of Nonrestoring Array Divider with Carry-Save and Carry Lookahead Techniques”,IFIP Proc. of VLSI ′85, Tokyo, 1985, pp. 243–251.

G. Metze and J.E. Robertson, “Elimination of Carry Propagation in Digital Computers”,Proc. International Conf. on Inf. Processing, Paris, 1959, pp. 389–396.

E. Lu et al., “A Programmable VLSI Architecture for Computing Multiplication and Polynomial Evaluation Modulo a Positive Integer”,IEEE Journ. on solid-State Circuits, vol. 23, 1988, pp. 204–207.

H. Schützeneder, “Entwurf eines Carry-Save-Modulo-Multiplizierers in CMOS-Technik”, Diploma Thesis, FH Munich, 1989.

J.E. Volder, “The CORDIC Trigonometric Computing Technique”,IRE Trans. on Electronic Computers, vol. EC-8, 1959, pp. 330–334.

R. Künemund et al., “CORDIC Processor with Carry-Save Architecture”,Proc. of ESSCIRC ′90, Grenoble, 1990, pp. 193–196.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Noll, T.G. Carry-save architectures for high-speed digital signal processing. J VLSI Sign Process Syst Sign Image Video Technol 3, 121–140 (1991). https://doi.org/10.1007/BF00927839

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/BF00927839