Abstract

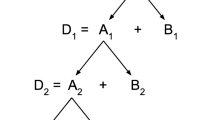

Modulo 2n+1 multiplication plays an important role in the Fermat number transform and residue number systems; the diminished-1 representation of numbers has been found most suitable for representing the elements of the rings. Existing algorithms for modulo (2n+1) multiplication either use recursive modulo (2n+1) addition, or a regular binary multiplication integrated with the modulo reduction operation. Although most often adopted for largen, this latter approach requires conversions between the diminished-1 and binary representations. In this paper we propose a parallel fine-grained architecture, based on a Wallace tree, for modulo (2n+1) multiplication which does not require any conversions; the use of a Wallace tree considerably improves the speed of the multiplier. This new architecture exhibits an extremely modular structure with associated VLSI implementation advantages. The critical path delay and the hardware requirements of the new multiplier are similar to that of a correspondingn×n bit binary multiplier.

Similar content being viewed by others

References

R.C. Agarwal and C.S. Burrus, “Fast convolution using Fermat number transforms with applications to digital filtering,”IEEE Trans. Acoust. Speech, Signal Processing, Vol. ASSP-22, pp. 87–97, 1974.

W. Luo, G.A. Jullien, N.M. Wigley, W.C. Miller, and Z. Wang, “An array processor for inner product computations using a Fermat number ALU,”Proc. 1995 Symposium on Application Specific Array Processors (in print).

L.M. Leibowitz, “A simplified binary arithmetic for the Fermat number transform,”IEEE Trans. Acoust. Speech, Signal Processing, Vol. ASSP-24, pp. 356–359, 1976.

W.K. Jenkins, “The design of specialized residue classes for efficient recursive digital filter realization,”IEEE Trans. Acoust. Speech, Signal Processing, Vol. ASSP-30, pp. 370–380, 1982.

W.K. Jenkins, “Recent advance in residue number techniques for recursive digital filtering,”IEEE Trans. Acoust. Speech, Signal Processing, Vol. ASSP-27, pp. 19–30, 1979.

F.J. Taylor, “A VLSI residue arithmetic multiplier”IEEE Trans. Comput., Vol. C-31, pp. 540–546, 1982.

J.J. Chang, T.K. Truong, H.M. Shao, I.S. Reed, and L.-S. Hsu, ‘The VLSI design of a single chip for the multiplication of integers modulo a Fermat number”,IEEE Trans. Acoust. Speech, Signal Processing, Vol. ASSP-33, pp. 1599–1602, 1985.

M. Benaissa, A Pajayakrit, S.S. Dlay, and A.G.J. Holt, “VLSI design for diminished-1 multiplication of integers modulo a Fermat number,”IEE Proc., Vol. 135, Pt. E, pp. 161–164, 1988.

M. Benaissa, A. Bouridane, S.S. Dlay, and A.G.J. Holt, “Diminished-1 multiplier for a fast convolver and correlator using the Fermat number transform,”IEE Proc., Vol. 135, Pt. G, pp. 187–193, 1988.

A.V. Curiger, H. Bonnenberg, and H. Kaeslin, “Regular VLSI architecture for multiplication modulo (2n+1),”IEEE J. Solid-State Circuits, Vol. 26, pp. 990–994, 1991.

A. Hiassat: “New memoryless mod (2n+1) residue multiplier,”Elec. Letts., Vol. 28, pp. 3124–3125, 1992.

C.S. Wallace, “A suggestion for a fast multiplier,”IEEE Trans. Electronic Computers, Vol. EC-13, pp. 14–17, 1964.

J.Y. Lee, H.L. Garvin, and C.W. Slayman, “A high-speed highdensity silicon 8×8-bit parallel multiplier,”IEEE J. Solid-State Circuits, Vol. SC-22, pp. 35–40, 1987.

Z. Wang, G.A. Jullien, and W.C. Miller, “New design techniques for column compression multipliers,”IEEE Trans. Comput., Vol. C-44, No. 8, pp. 962–970, 1995.

R.P. Brent and H.T. Kung, “A regular layout for parallel adders,”IEEE Trans. Comput., Vol C-31, pp. 260–264, 1982.

V.G. Oklobdzija, D. Villeger, and S.S. Liu, “A method for speed optimized partial product reduction and generation of fast parallel multiplier using an algorithmic approach,”IEEE Trans. Computers., Vol. C-45, No. 3, pp. 294–306, 1996.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Wang, Z., Jullien, G.A. & Miller, W.C. An efficient tree architecture for modulo 2n+1 multiplication. J VLSI Sign Process Syst Sign Image Video Technol 14, 241–248 (1996). https://doi.org/10.1007/BF00929618

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/BF00929618