Abstract

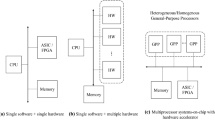

Hardware/Software co-design is an increasingly common design style for integrated circuits. It allows the majority of a system to designed quickly with standardized parts, while special purpose hardware is used for the time critical portions of the system. The framework considered in this paper performs Hardware/Multi-Software (HMS) co-design for iterative loops, given an input specification that includes the system to be built, the number of available processors, the total chip area, and the required response time. Originally, all operations are done in software. The system then substitutes hardware (adder, multiplier, bus) for software based on theneedability of each type of hardware unit. After a new hardware unit is introduced the system is rescheduled using a variation of rotation scheduling in which operations may be moved between processors. Experimental results are shown that illustrate the efficiency of the algorithms as well as the savings achieved.

Similar content being viewed by others

References

D. Gaski, F. Vahid, S. Narayan, and J. Gong, “Specification and design of embedded systems,” Prentice-Hall, Inc, Englewood Cliffs, NJ, 1994.

B. Bose, M.E. Tuna, and S.D. Johnson, “System factorization in codesign: A case study of the use of formal techniques to achieve hardware-software decomposition,”Proceedings of the International Conference on Computer Design, pp. 458–461, Oct. 1993.

B. Bose, M.E. Tuna, and S.D. Johnson, “Continuations in hardware-software codesign,”Proceedings of the International Conference on Computer Design, pp. 264–269, Oct. 1994.

P. Chou, R.B. Ortega, and G. Borriello, “Interface co-synthesis techniques for embedded systems,”Proceedings of the International Conference on Computer-Aided Design, pp. 566–72, Nov, 1995.

T.-Y. Yen and W. Wolf “Communication synthesis for distributed embedded systems,”Proceedings of the International Conference on Computer-Aided Design, pp. 288–294, Nov. 1995.

J.P. Calvez and O. Pasqueir, “Performance assessment of embedded hw/Sw systems,”Proceedings of the International Conference on Computer Design, pp. 52–57, Oct. 1995.

T.-Y. Yen and W. Wolf, “Performance estimation for real-time distributed embedded systems,”Proceedings of the International Conference on Computer Design, pp. 64–694, Oct. 1995.

A. Wolfe, “A case study in low-power system-level design,”Proceedings of the International Conference on Computer-Aided. Design, pp. 332–338, Oct. 1995.

S. Antoniazzi, A. Balboni, W. Fornaciari, and D. Sciuto, “HW/SW codesign for embedded telecom systems,”Proceedings of the International Conference on Computer Design, pp. 278–281, Oct. 1994.

B.K. Holmer and B.M. Prangle, “Hardware/software codesign using automated instruction set design & processor synthesis,” Technical Report CS-93-14, Pennsylvania State University, Department of Computer Science, 1993.

J. Henkel, T. Benner, and R. Ernst, “Hardware generation and partitioning effects in the COSYMA system,”2nd International Workshop on Hardware-Software Co-Design, Workshop Handout, 1993.

T. Benner, R. Ernst, I. Koenenkamp, P. Schueler, and H.-C. Schuab, “Prototyping system for verification and evaluation in hardware-software cosynthesis,”Proceedings of the 6th IEEE International Workshop on Rapid System Prototyping pp. 54–59, 1995.

R. Gupta and G. DeMicheli, “Hardware-software cosynthesis for digital systems,”IEEE Design and Test of Computers pp. 29–41, Oct. 1993.

R. Gupta and G. DeMicheli, “System level synthesis using reprogramable components,”The European Conference on Design Automation, pp. 2–7, Mar. 1992.

C.E. Leiserson and J.B. Saxe, “Retiming synchronous circuitry,”Algorithmica, Vol. 6, pp. 5–35, 1991.

L.-F. Chao, A. LaPaugh, and E.H.-M. Sha, “Rotation scheduling: A loop pipelining algorithm”Proc. 30th ACM/IEEE Design Automation Conference, pp. 566–572, June 1993.

M. Sheliga and E.H.-M. Sha, “Bus minimization and scheduling of multi-chip modules,”The 1995 Great Lakes Symposium on VLSI, Buffalo, NY, pp. 40–45, Mar. 1995.

M.R. Garey and D.S. Johnson, “Computers and intractability —A guide to the theory of NP-completeness,” W.H. Freeman and Company, New York, NY, 1979.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Sheliga, M., Hsing-Mean Sha, E. Hardware/Software co-design with the HMS framework. J VLSI Sign Process Syst Sign Image Video Technol 13, 37–56 (1996). https://doi.org/10.1007/BF00930666

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/BF00930666