Abstract

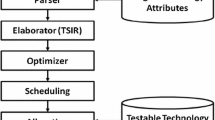

This article discusses the cooperation of testability and High Level Data Path Synthesis (HLDPS). A particular target domain, namely real time digital signal processing, is addressed where the generation of customized data path compositions is one of the crucial steps during the HLDPS. Taking the testability cost into account during the HLDPS strongly depends on the test generation tool in use. It requires a test tool for which the capabilities have to be amenable to modeling on a high level. For this purpose, a novel sympolic test pattern approach is presented which is based on symbolic controllability and observability descriptions. These symbolic descriptions are calculated on the building block level and are also very useful for analyzing the testability problems in an early stage of the HLDPS. Our experiments show that the calculation and evaluation of these descriptions is very efficient and fast enough for the HLDPS to explore many data path alternatives.

Similar content being viewed by others

References

M.C. McFarland, A.C. Parker, and R. Camposano, “Tutorial on high-level synthesis,”Proc. 25th ACM/IEEE Design Automation Conference, pp. 330–336, June 1988.

H. De Man, F. Catthoor, G. Goossens, J. Vanhoof, J. Van Meerbergen, and J. Huiskens, “Architecture driven synthesis techniques for mapping digital processing algorithms into silicon,”Special Issue of the Proceedings of the IEEE devoted to CAD, vol. 78, pp. 319–336, February 1990.

S. Lin, C.A. Njinda and M.A. Breuer, “A systematic approach for designing testable VLSI circuits,”Proc. Int. Conf. on Comp.-Aided Design, pp. 496–499, November 1991.

C.A. Papachristou, S. Chiu and H. Harmanani, “A data path synthesis method for self-testable designs,”Proc. 28th ACM/IEEE Design Auto. Conf., pp. 378–384, June 1991.

L. Goldstein and E. Thigpen, “SCOAP: Sandia Controllability/ Observability Analysis Program,”Proc. 17th ACM/IEEE Design Auto. Conf., pp. 190–196, June 1980.

C.H. Chen and P.R. Menon, “An approach to functional level testability analysis,”Proc. Int. Test Conf., paper 18.1, pp. 373–380, August 1989.

S. Freeman, “Test generation for data-path logic: The F-path method,”IEEE Journal of Solid-State Circuits, vol. 23 pp. 421–427, April 1988.

B.T. Murray and J.P. Hayes, “Hierarchical test generation using precomputed tests for modules,”Proc. Int. Test Conf, pp. 221–229, September 1988.

P.N. Anirudhan and P.R. Menon, “Symbolic test generation for hierarchical modelled digital systems,”Proc. Int. Test Conf., pp. 461–469, August 1989.

J. van Sas, F. Catthoor, P. Vandeput, F. Rossaert and H. De Man, “Automated test pattern generation for the Cathedral-II/2nd architectural synthesis environment,”Proc. European Design Auto. Conf., Amsterdam, pp. 208–213, February 1991.

H. Hofestädt and M. Gerner, “Qualitative testability analysis and hierarchical test pattern generation: A new approach to design for testability,”Proc. Int. Test. Conf., pp. 538–546 September 1987.

A. Gosh, S. Devadas, A.R. Newton, “Sequential test generation at the register-transfer and logic levels,”Proc. 27th ACM/IEEE Design Auto. Conf., pp. 580–586, June 1990.

J. Steensma, F. Catthoor and H. De Man, “Test of high throughput data paths using symbolic controllability and observability description,”6th Workshop On New Directions For Testing, Montreal, Canada, pp. 67–76, May 21–22, 1992.

D. Lanneer, S. Note, F. Depuydt, M. Pauwels, F. Catthoor, G. Goossens, and H. De Man, “Architectural synthesis for medium and high throughput signal processing with the new Cathedral environment,” inTrends in high-level synthesis, (eds. R. Camposano and W. Wolf), Boston: Kluwer, 1991.

S. Note, F. Catthoor, J. Van Meerbergen and H. De Man, “Definition and assignment of complex data-paths suited for high throughput DSP applications,”Proc. Int. Conf. on Computer Aided Design, pp. 108–111, November 1989.

W. Geurts, F. Catthoor and H. De Man, “Time constrained allocation and assignment techniques for high throughput signal processing,”Proc. 29th ACM/IEEE Design Auto. Conf., pp. 124–127, June 1992.

F. Catthoor, J. Van Sas, L. Inze and H. De Man, “A test strategy for multiprocessor architectures,”IEEE Design and Test of Computers, vol. 6, pp. 18–34, April 1989.

E. Blokken, H. DeKeulenaer, F. Catthoor and H. DeMan, “A Flexible module library for custom DSP applications in a multiprocessor environment,” IEEE Journal of Solid State Circuits, vol. 25, pp. 720–729, June 1990.

J. Rajski and J. Vasuderamurthy, “Testability preserving transformations in multi-level logic synthesis,”Proc. Int. Test. Conf., pp. 265–273, September 1990.

S. Devadas and K. Keutzer, “Synthesis of robust delay-faulttestable circuits: Practice,”IEEE Transactions on Computer-Aided Design, vol. 11, pp. 277–300, March 1992.

F. Brglez, D. Bryan, J. Calhoun, G. Kedem and R. Lisanke, “Automated synthesis for testability,”IEEE Trans. on Industrial Electronics vol. 36, pp. 263–277, May 1989.

F.P.M. Beenker, K.J.E. Eerdewijk, R.B.W. Gerritsen, F.N. Peacock and M. van der Star, “Macro testing: Unifying IC and board test,”IEEE Design and Test of Computers, vol. 3, pp. 26–32, December 1986.

P.E.R. Lippens, J.L. Meerbergen, A. van der Werf, W.F.J. Verhaegh, B.T. McSweeney, J.O. Huisken and O.P. McArdle, “PHIDEO: A silicon compiler for high speed algorithms,”Proc. European Design Auto. Conf., Amsterdam, pp. 436–441, February 1991.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Steensma, J., Geurts, W., Catthoor, F. et al. Testability analysis in high level data path synthesis. J Electron Test 4, 43–56 (1993). https://doi.org/10.1007/BF00971939

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF00971939