Abstract

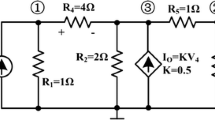

Analog circuit testing is considered to be a very difficult task. This difficulty is mainly due to the lack of fault models and accessibility to internal nodes. To overcome this problem, an approach is presented for analog circuit modeling and testing. The circuit modeling is based on first-order sensitivity computation. The testability of the circuit is analyzed by the multiple-fault model and by functional testing. Component deviations are deduced by measuring a number of output parameters, and through sensitivity analysis and tolerance computation. Using this approach, adequate tests are identified for testing catastrophic and soft faults. Some experimental results are presented for simple models as well as multiple-fault models.

Similar content being viewed by others

References

L. Milor and V. Visavanathan, “Detection of catastrophic faults in analog circuits,”IEEE Trans. Comput. Aided Design, Vol. CAD-8, No. 2, pp. 114–130, 1989.

K.R. Chin, “Functional testing of circuits and SMD bords with limited nodal access,” inInt. Test. Conf., Los Alamitos, CA, pp. 129–143, 1989.

H. Dai and M. Sounders, “Time-domain testing strategies and fault diagnosis for analog systems,”IEEE Trans. Instrum. Measure., Vol. 39, No. 1, pp. 157–162, 1990.

P.P. Fasang, D. Mullins, and T. Wong, “Design for testability for mixed analog/digital ASICs,“IEEE Custom Integrated Circuits Conf., pp. 16.5.1–16.5.4, 1988.

Naim Ben Hamida and Bozena Kaminska, “Analog circuit testing based on sensitivity computation and new circuit modeling,” inInt. Test Conf., Baltimore, 1993.

Mustapha Slamani and Bozena Kaminska, “Analog circuit fault diagnosis based on sensitivity computation and fault testing,”IEEE Design Test Comput., pp. 30–39, March 1992.

Mustapha Slamani and Bozena Kaminska, “Testing analog circuits by sensitivity computation,” inEuropean Design Automation conf., Paris, pp. 532–537, Paris, 1992.

A.L. Rosenblum, and M.S. Ghaussi, “Multiparameter sensitivity problem in active RC networks,”IEEE Trans. Circuit Theory, Vol. CT-18, No. 6, pp. 592–599, 1971.

P. Duhamel and J.C. Rault, “Automatic test generation techniques for analog circuits and systems: a review,”IEEE Trans. Circuits Syst., Vol. CAS-26, No. 7, pp. 411–439, 1979.

W.J. Butler and S.S. Haykin, “Multiparameter sensitivity problems in network theory,”Proc. IEEE, Vol. 117, No. 12, pp. 2228–2236, 1970.

J.K. Fidler, “Differential-incremental-sensitivity relationships,”Electron. Lett., Vol. 20, No. 10, pp. 626–627, 1984.

Erich Wehrhahn, “Hierarchical circuit analysis,” inInt. Symp. Circuits and Systems, pp. 701–704, 1989.

HSPICE User's Manual: H8801, Meta-Software, Inc. 1988.

LINDO User's Manual, 4th ed., “Linear, and Quadratic Programming with LINDO,” Linus Schrage.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Hamida, N.B., Kaminska, B. Multiple fault analog circuit testing by sensitivity analysis. J Electron Test 4, 331–343 (1993). https://doi.org/10.1007/BF00972158

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF00972158