Abstract

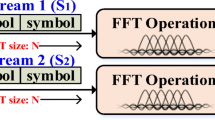

This paper discusses the implementation of a pipelined architecture for implementing large block size Winograd FFTs. The advantages of using the Winograd over the Cooley-Tukey radix-2 FFT are discussed and some estimates of possible power consumption of a silicon implementation of the architecture are made.

Similar content being viewed by others

References

S. Winograd, “On Computing the Discrete Fourier Tramsform”, Math. Comp.32, 175–199, 1978.

S.J. Campanella and S. Sayegh, “A flexible on-board demultiplexer/demodulator”, 12th AIAA International Communication Satellite Systems Conference, Arlington, VA, USA, 299–303, 1988.

S.K. Barton and Y.O. Al-Jalili, “A multi-carrier demodulator architecture for SMS/IBS”, International Journal of Satellite Communications11, 287–298, 1993.

S.K. Barton, P.L. Field, M. Shahid, S.J. Shepherd, and C.W. Wyatt-Millington, “Study of Multicarrier Demodulator with Frequency-Domain Symbol Timing Correction”, final report under ESA Purchase Order No. 130028, 1994.

R.E. Blahut, Fast Algorithms for Digital Signal Processing, Addison Wesley, 1985.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Wyatt-Millington, W., Shepherd, S. & Barton, S. A pipelined implementation of the Winograd FFT for satellite on-board multi-carrier demodulation. Wireless Pers Commun 2, 321–334 (1995). https://doi.org/10.1007/BF01099339

Issue Date:

DOI: https://doi.org/10.1007/BF01099339