Abstract

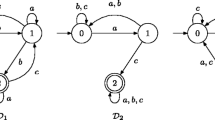

The increase of computational power due to additions of some horizontal interconnections between neighboring nodes of binary trees is investigated using the concept of systolic automata over so-called 7-trees with one-directional, bottom-to-root, flow of computation.Y-trees are obtained from binary trees by connecting some neighboring pairs of nodes at the same level that are not brothers.

We introduce the concept of systolic automata on regularY-trees in column normal form and prove that any systolic automaton on regularY-trees is equivalent to one in the column normal form. We then fully characterize those regularY-trees over which the class of languages recognized by nondeterministic automata is the same as for deterministic automata. An analogous result is obtained for stability. Furthermore, we show that superstable deterministic systolic automata over regularY-trees recognize only regular languages. Finally, several closure properties of and relations between classes of languages accepted by systolic automata over differentY-trees are studied.

Similar content being viewed by others

References

A. Cerny, J. Gruska, Modular real-time trellis automata,Fundamenta Informaticae IX:253–282, 1986.

P. Chuavalee, L. N. Bhuyan, VLSI layout of binary structures,Integration of VLSI Journal,6:83–99, 1989.

K. Culik II, J. Gruska, A. Salomaa, Systolic automata for VLSI on balanced tree,Acta Informatica 18:335–344, 1983.

K. Culik II, J. Gruska, A. Salomaa, On a family of L languages resulting from systolic tree automata,Theoretical Computer Science 23:231–242, 1983.

K. Culik II, J. Gruska, A. Salomaa, Systolic trellis automata,International Journal Computer Mathematics 15:195–212, 1984, and16:3–22, 1984.

K. Culik II, J. Gruska, A. Salomaa, Systolic trellis automata: stability, decidability and complexity,Information and Control 71:218–230, 1986.

K. Culik II, H. Jürgensen, Programmable finite automata for VLSI,International Journal of Computer Mathematics 14:259–275, 1983.

K. Culik II, A. Salomaa, D. Wood, Systolic tree acceptors, RAIROInformatique Théorique 18:53–69, 1984.

A. Despain, D. Patterson, X-tree: A structured multiprocessor computer architecture, inProceedings of the 5th Annual Symposium on Computer Architecture, pages 144–151. IEEE, New York, 1978.

C. R. Dyer, One way bounded cellular automata,Information and Control 44:261–281, 1980.

E. Fachini, R. Francese, M. Napoli, D. Parente, BC-tree systolic automata: characterization and properties,Computers and Artificial Intelligence 8(1):53–82, 1989.

E. Fachini, A. Maggiolo Schettini, G. Resta, D. Sangiorgi, Some structural properties of systolic tree automata,Fundamenta Informaticae XII:571–585, 1989.

E. Fachini, A. Maggiolo Schettini, D. Sangiorgi, Classes ofY-tree systolic automata and systolic trellis automata,Acta Informatica 29(6/7):623–643, 1992.

E. Fachini, A. Monti, A Kleene-like characterization of languages accepted by systolic binary tree automata,Journal of Computer and System Science, to appear (1994).

E. Fachini, A. Monti, Regular sets, context-free languages and systolicY-tree automata, inProceedings of the 4th Italian Conference of Theoretical Computer Science, pages 199–213. World Scientific 1993.

E. Fachini, A. Monti, M. Napoli, D. Parente, Languages accepted by systolicY-tree automata: structural characterization,Acta Informatica 29(8):761–778, 1992.

E. Fachini, M. Napoli, C-tree systolic automata,Theoretical Computer Science 56:155–186, 1988.

J. Gruska, Synthesis, structure and power of systolic computations,Theoretical Computer Science 71:47–78, 1990.

O. H. Ibarra, S. M. Kim, Characterization and computational complexity of systolic trellis automata,Theoretical Computer Science 29:123–153, 1984.

O. H. Ibarra, S. M. Kim, A characterization of systolic binary tree automata and applications,Acta Informatica 21:193–207, 1984.

A. Monti, D. Parente, Systolic tree with base automata,Internationaljournal of Foundations of Computer Science 2(3):221–235, 1991.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Fachini, E., Gruska, J., Napoli, M. et al. Power of interconnections and of nondeterminism in regularY-tree systolic automata. Math. Systems Theory 28, 245–266 (1995). https://doi.org/10.1007/BF01303058

Received:

Revised:

Accepted:

Issue Date:

DOI: https://doi.org/10.1007/BF01303058