Abstract

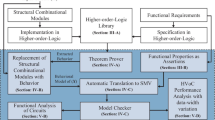

Faced with the challenge of designing correct circuits, the research community has been applying alternative verification methodologies istead of only traditional methods like ad hoc simulation. The best choice among alternatives like tautology checking, symbolic simulation, and theorem proving depends very theorem proving is best applicable, one is faced with the problem of choosing a formalism. This article compares the proof assistant HOL and the theorem-prover Boyer-Moore based on a practical experience with both systems in order to verify a combinatorial and parameterized hardware module from the CATHEDRAL II Silicon Compiler library. Although the comparison is based on a specific application, the general features, advantages, and drawbacks of both systems are discussed, with consideration given to the verification of other kinds of circuits.

Similar content being viewed by others

References

H. De Man, J. Rabaey, P. Six, and L. Claesen. Cathedral-II: a silicon compiler for digital signal processing.IEEE Design & Test of Computers, 3(6):73–85 (December 1986)

S. M. German, and Y. Wang. Formal verification of parameterized hardware designs.Proceedings IEEE International Conference on Computer Design: VLSI in Computers, ICCD-85, October 1985, pp. 549–552.

M. Gordon. HOL: a proof generating system for higher-order logic.VLSI Specification, Verification and Synthesis, G. Birtwistle and P.A. Subrahmanyam (eds.). Academic Press, Boston, 1988, pp. 73–127.

R.S. Boyer and J.S. Moore.A Computational Logic Handbook. Academic Press, New York, 1988.

C. Mead, and L. Conway.Introduction to VLSI Systems. Addison-Wesley, Reading, MA, 1980, pp. 150–154.

D. Verkest, L. Claesen, and H. De Man. Correctness proofs of parameterized hardware modules in the Cathedral-II synthesis environment.European Design Automation Conference EDAC 90. IEEE Computer Society Press, pp. 62–66.

C.M. Angelo, L. Claesen, and H. De Man. A methodology for proving correctness of parameterized hardware modules in HOL.CHDL'91, IFIP, Tenth International Symposium on Computer Hardware Description Languages and their Applications, D. Borrione and R. Waxman (eds.). Elsevier/North Holland, April, 1991, Marseille, France, pp. 43–62.

V. Stavridou, H. Barringer, and D.A. Edwards. Formal specification and verification of hardware: a comparative case study.25th ACM/IEEE Design Automation Conference, 1988, pp. 197–203.

B. Levy. An overview of hardware verification using the state delta verification system.1991 International Workshop on Formal Methods in VLSI Design, Jan 9–11, 1991, Miami, FL.

J.M. Wing. A specifier's introduction to formal methods.IEEE Computer magazine, 23(9):8–24 (September 1990).

M. Gordon. Why higher-order logic is a good formalism for specifying and verifying hardware.Formal Aspects of VLSI Design G. Milne and P.A. Subrahmanyam, (eds.). North Holland, Amsterdam, 1986, pp. 153–178.

A.J. Camilleri, M. Gordon, and T. Melham. Hardware verification using higher-order logic.From HDL Descriptions to Guaranteed Correct Circuit Designs. D. Borrione (ed.). Elsevier Science Publishers B.V., North Holland, IFIP 1987, pp. 43–67.

G. Cousineau, M. Gordon, G. Huet, R. Milner, L. Paulson, and C. Wadsworth,The ML Handbook. INRIA, France 1986.

R.S. Boyer, and J.S. Moore,A Computational Logic. Academic Press, New York, 1979.

J.J. Joyce.Multi-Level Verification of Microprocessor Based Systems. Ph.D. thesis, Computer Laboratory, Cambridge University, December 1989.

P.J. Windley, Abstract hardware.Proceedings of the ACM/SIGDA International Workshop in Formal Methods in VLSI Design, Miami, FL. January 1991.

S-K. Chin. Verified synthesis functions for negabinary arithmetic hardware.IMEC-IFIP International Workshop on Applied Formal Methods for Correct VLSI Design I, Belgium, November 1989, L. Claesen, (ed.). Elsevier Science Publishers, Amsterdam pp. 226–235.

W.F. Clocksin. Logic programming and digital circuit analysis.The Journal of Logic Programming, 4:59–82 (1987).

A.J. Camilleri. Simulation as an aid to verification using the HOL theorem prover.Design Methodologies for VLSI and Computer Architecture, D.A. Edwards, (ed.). Elsevier Science Publishers B.V., North-Holland, IFIP, 1989 pp. 147–168

T.F. Melham. Abstraction mechanisms for hardware verification.VLSI Specification, Verification and Synthesis: Proceedings of the Hardware Verification Workshop Calgary, Canada, 12–16 January 1987, G. Birtwistle and P.A. Subrahmanyam (ed.). Kluwer Academic Publishers, Boston, 1988, pp. 267–291.

J. Herbert. Formal reasoning about the timing and function of basic memory devices.Formal VLSI Correctness Verification, VLSI Design Methods II, L. Claesen, (ed.). Elsevier Science Publishers B.V., North-Holland, IFIP 1990, pp. 379–398.

W.A. Hunt.FM8501, a verified microprocessor Ph.D. thesis, Department of Computer Sciences, University of Texas at Austin, TX, 1985.

L. Pierre. The formal proof of sequential circuits described in CASCADE using the Boyer-Moore theorem prover.Formal VLSI Correctness Verification, VLSI Design Methods II, L. Claesen, (ed.). Elsevier Science Publishes, North Holland, 1990, pp. 309–328.

T.F. Melham. Automating recursive type definitions in higher order logic.Current Trends in Hardware Verification and Automated Theorem Proving, G. Birtwistle and P.A. Subrahmanyam, (eds.). Springer-Verlag, New York, 1989, pp. 341–386.

T.F. Melham. Using recursive types to reason about hardware in higher order logic.The Fusion of Hardware Design and Verification: Proceedings of the IFIP WG 10.2 Working Conference, Glasgow, July 1988, G.J. Milne (ed.). North-Holland, Amsterdam, pp. 27–50.

B.C. Brock and W.A. Hunt, Jr. The formalization of a simple hardware description language.IMEC-IFIP International Workshop on Applied Formal Methods for Correct VLSI Design II, Belgium, November 1989, L. Claesen, (ed.). Elsevier Science Publishers, Amsterdam, pp. 778–793.

B.C. Brock, and W.A. Hunt, Jr. A formal introduction, to a, simple HDL.Formal Methods for VLSI Design, IFIP, 1990, J. Staunstrup (ed.) Elsevier Science Publishers, Amsterdam, pp. 285–329.

R. Boulton, M. Gordon, J. Herbert, and J. Van Tassel. The HOL verification of ELLA designs.Proceedings of the International Workshop on Formal Methods in VLSI Design, Miami, 1991.

J.D. Morison, N.E. Peeling, and T.L. Thorp. ELLA: hardware description or specification?Proceedings of the IEEE International Conference, CAD-84, Santa Clara, CA, November 1984.

Institute of Electrical and Electronics Engineers,IEEE Standard VHDL Language Reference Manual. IEEE Press, New York, 1988.

P.N. Hilfinger, Silage, a high-level language and silicon compiler for digital signal processing.Proceedings IEEE CICC-85, Portland, OR, May 1985, pp. 213–216.

A.D. Gordon. A mechanised definition of silage in HOL. Internal report, Computer Laboratory, University of Cambridge, February 1992.

C.M. Angelo, L. Claesen, and H. De Man The formal semantics definition of a multi-rate DSP specification language in HOL. To appear in the Proceedings ofHOL'92 International Workshop on Higher Order Logic Theorem Proving and Its Applications L. Claesen and M. Gordon (eds.). Elsevier/North Holland, Leuven, Belgium, September 1992

M. Kaufmann. A user's manual for an interactive enhancement to the Boyer-Moore theorem prover.Technical Report, 19, Computational Logic Inc., Austin, TX, May 1988.

M. Kaufmann. DEFN-SK: an extension of the Boyer-Moore theorem prover to handle first-order quantifiers.Technical Report 43, Computational Logic Inc., Austin, TX, May 1989. To appear in theJournal of Automated Reasoning.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Angelo, C.M., Verkest, D., Claesen, L. et al. On the comparison of HOL and Boyer-Moore for formal hardware verification. Form Method Syst Des 2, 45–72 (1993). https://doi.org/10.1007/BF01383943

Issue Date:

DOI: https://doi.org/10.1007/BF01383943