Abstract

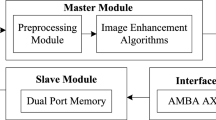

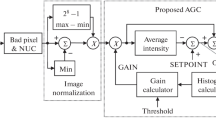

This paper describes an image processing system using Image Signal Multiprocessors (ISMPs) adapted to gray-level image preprocessing for image analysis and image enhancement. It is composed of four ISMPs, five 1H-delay-lines, two 512×512×8-bit frame memories, a video timing controller (VTC), two 256-word ×8-bit ×8-table Look Up Tables (LUTs) and 80 nsec/sampling A/D and D/A converters. This multiprocessor system performs convolution operations such as spatial filters, contrast enhancement, and binarization for gray-level images, thinning, thickening, pattern matching etc. for binary images, and image quality improvement for moving images such as T.V. images. Otherwise, it performs feature extraction operations such as area calculations, fillet coordination, and moment calculations for objective image data. Moreover, this system is capable of applying color image processing by using a multiboard system.

Similar content being viewed by others

References

Fukushima, Y. Kobayashi, K. Hirasawa, and T. Bandoh, “An image signal processor,” ISSCC Dig. Tech. Papers, 1983, pp. 258–259.

T. Nukiyama, et al., “A VLSI image pipeline processor,”ISSCC Dig. Tech. Paper, 1984, pp. 208–209.

A. Kanuma, et al., “A 20MHz pipelined CMOS image processor,”ISSCC Dig. Tech. Papers, 1986, pp. 102–103.

Y. Kobayashi, et al., “A BiCMOS image signal processor with line memories,”ISSCC Dig. Tech. Papers, 1987, pp. 182–183.

T. Mori, et al., “A micro-programmable real-time image processor,”ISSCC Dig. Tech. Papers, 1986, pp. 144–145.

K. Aono, et al., “A real-time image signal processor with micro-programmable and expandable architecture,”Proc. ESSCIRC'86, 1986, pp. 98–100.

M. Maruyama, et al., “A 200MIPS image signal multiprocessor on a single chip,”ISSCC Dig. Tech. Papers, 1990, pp. 122–123.

T. Nishitani, et al., “Parallel video signal processor configuration based on overlap-save technique and its LSI processor element: VISP,”Journal of VLSI Signal Processing, vol. 1, 1989, pp. 25–34.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Nakahira, H., Maruyama, M., Ueda, H. et al. An image processing system using Image Signal Multiprocessors (ISMPs). J VLSI Sign Process Syst Sign Image Video Technol 5, 133–140 (1993). https://doi.org/10.1007/BF01581290

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/BF01581290