Abstract

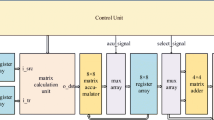

A MIMD based multiprocessor architecture for real-time video processing applications consisting of identical bus connected processing elements has been developed. Each processing element contains a RISC processor for controlling and data-dependent tasks and a Low Level Coprocessor for fast processing of convolution-type video processing tasks. To achieve efficient parallel processing of video input signals, the architecture supports independent processing of overlapping image segments. Running at a clock rate of 40 MHz, a single processing element provides a peak performance of 640 Mega arithmetic operations per second (MOPS). For the real-time processing of basic video processing tasks like 3×3 FIR-filter, 8×8 2D-DCT and motion estimation, a single processing element provides a sufficient computational rate for video signals with Common Intermediate Format (CIF) at a frame rate up to 30 Hz. For hybrid source coding of CIF video signals at a frame rate of 30 Hz a multiprocessor system consisting of six processing elements is required. A linear speedup of the multiprocessor system compared to a single processing element is achieved. A VLSI implementation of a processing element in 0.8 µm CMOS technology is under development.

Similar content being viewed by others

References

CCITT Study Group XV, “Recommendation H.261, Video Codec for Audiovisual Services at p×64 kbit/s,” Report R37, Geneva, July 1990.

CCIR Recommendation 601, “Encoding parameters of digital television for studios,” inRecommendations and Reports of the CCIR, vol. 11, pt. 1, ITU 1982, Geneva, Switzerland.

CCIR, “Draft new report AD/CMTT on digital transmissions of component coded television signals at 30–34 Mbit/s and 45 Mbit/s” CCIR Document (1986–1990) CMTT/116.

H. Yasuda, “Standardization activities on multimedia coding in ISO,”Signal Processing: Image Communications, vol. 1, 1989, pp. 3–16.

ISO-IEC JTC1/SC2/WG11 MPEG-90/176 Rev. 2 1990.

M.L. Liou and H. Fujiwara, “VLSI implementation of a low bit-rate video codec,”Proc. of IEEE International Symposium on Circuits and System, 1991, pp. 180–183.

H. Yamauchi, et al., “Architecture and Implementation of a highly parallel single-chip video DSP,”IEEE Transactions on Circuits and Systems for Video Technology, vol. 2, 1992, pp. 207–220.

T. Micke, D. Müller, R. Heiss, “ISDN-Bildtelefon auf der Grundlage eines Array-Processor-IC,”mikroelektronik, vde-verlag, vol. 5, 1991, pp. 116–119.

I. Tamitani, et al., “A real-time video signal processor suitable for motion picture coding applications,”IEEE Transactions on Circuits and Systems, vol. 36, 1989, pp. 1259–1266.

Integrated Information Technology, Inc., “IIT Vision Processor,” Preliminary Data Sheet, Santa Clara, September 1991.

T. Nishitani, et al., “Parallel Video Signal Processor Configuration based on Overlap-Save Technique and its LSI Processor Element: VISP,”Journal of VLSI Signal Processing, vol. 1, 1989, pp. 25–34.

P. Pirsch and T. Wehberg, “VLSI architecture of a programmable real-time video signal processor,”Proc. of SPIE Conf. Digital Image Processing and Visual Communication Technologies in the Earth and Atmospheric Sciences, SPIE vol. 1301, 1990, pp. 2–12.

IEEE CAS Standards Committee, “Draft Standard Specification for the Implementation of 8 × 8 Inverse Discrete Cosine Transform,” P1180/D2, July 1990.

U. Totzek and F. Matthiesen, “Two-dimensional discrete cosine transformation with linear systolic arrays,”Systolic Array Processors, pp. 388–397, New York: Prentice Hall, 1989.

H. Jeschke, K. Gaedke, and P. Pirsch, “A VLSI based multiprocessor architecture for video signal processing,”International Symposium on Circuits and Systems, vol. 4, 1992, pp. 1685–1688.

H.G. Musmann, P. Pirsch, and H.-J. Grallert, “Advances in picture coding“,Proc. IEEE, vol. 73, 1985, p. 523–548.

H. Jeschke, H. Volkers, and T. Wehberg, “A multiprocessor system for real-time image processing based on a MIMD architecture,” in H. Burkhardt, et al., (Eds.),Proc. of the Workshop From Pixels to Features II, 1990, p. 173–185, North-Holland: Elsevier, 1991.

K. Gaedke, H. Jeschke, and T. Wehberg, “Architecture and application of a SIMD based processing element for real-time image processing,”Proc. of the ISMM International Workshop PARALLEL COMPUTING, pp. 382–385, ACTA PRESS, 1991.

H. Jeschke, K. Gaedke, and P. Pirsch, “Multiprocessor performance for real-time processing of video coding applications,”IEEE Transactions on Circuits and Systems for Video Technology, vol. 2, 1992, pp. 221–230.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Gaedke, K., Jeschke, H. & Pirsch, P. A VLSI based MIMD architecture of a multiprocessor system for real-time video processing applications. J VLSI Sign Process Syst Sign Image Video Technol 5, 159–169 (1993). https://doi.org/10.1007/BF01581293

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/BF01581293