Abstract

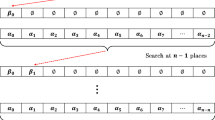

Thearea-time complexity of VLSI computations is constrained by the flow and the storage of information in the two-dimensional chip. We study here the information exchanged across the boundary of the cells of asquare-tessellation of the layout. When the information exchange is due to thefunctional dependence between variables respectively input and output on opposite sides of a cell boundary, lower bounds are obtained on theAT 2 measure (which subsume bisection bounds as a special case). When information exchange is due to thestorage saturation of the tessellation cells, a new type of lower bound is obtained on theAT measure.

In the above arguments, information is essentially viewed as a fluid whose flow is uniquely constrained by the available bandwidth. However, in some computations, the flow is kept below capacity by the necessity to transform information before an output is produced. We call this mechanismcomputational friction and show that it implies lower bounds on theAT/logA measure.

Regimes corresponding to each of the three mechanisms described above can appear by varying the problem parameters, as we shall illustrate by analyzing the problem of sortingn keys each ofk bits, for whichAT 2,AT, andAT/logA bounds are derived. Each bound is interesting, since it dominates the other two in a suitable range of key lengths and computations times.

Similar content being viewed by others

References

C. D. Thompson,A Complexity Theory for VLSI, Ph.D. Thesis, Dept. of Comp. Science, Carnegie-Mellon University; August 1980.

R. B. Johnson, “The complexity of a VLSI adder,”Information Processing Letters, vol. 11, n. 2, pp. 92–93; October 1980.

G. M. Baudet, “On the area required by VLSI circuits,” in H. T. Kung, R. Sproull, and G. Steele (eds.),VLSI Systems and Computations, pp. 100–107, Computer Science Press, Rockville, MD; 1981.

Z. Kedem, “Optimal allocation of computational resources in VLSI,”Proc. 23rd Annual Symposium on the Foundations of Computer Science, Chicago, IL, pp. 379–386; November 1982.

A. El Gamal, J. W. Greene, and K. F. Pang, “VLSI complexity of coding,”Proceedings 1984 Conference on Advanced Research in VLSI, M.I.T., Cambridge, MA; January 1984.

D. Angluin, “VLSI; On the merits of batching,”manuscript; April 1982.

A. Siegel, “Minimal storage sorting circuits,”IEEE Trans, on Comput., vol. C-34, n. 4; April 1985.

S. E. Hambrush and J. Simon, “Solving undirected graph problems on VLSI,”CS-81-23,Computer Science Department, Pennsylvania State Univ., Univ. Park, PA, December 1981.

J. Ja'Ja', “The VLSI complexity of selected graph problems,”Journal of the ACM, Vol. 31, No. 2, pp. 377–391; April 1984.

A. C. C. Yao, “Some complexity questions related to distributive computing,”Proc. 11th Annual ACM Symposium on Theory of Computing, Atlanta, GA, pp. 209–213; April 1979.

A. C. C. Yao, “The entropie limitations on VLSI computations,”Proc. 13th Annual ACM Symposium on Theory of Computing, Milwaukee, WI, pp. 308–311; April 1981.

J. Ja'Ja' and V. K. P. Kumar, “Information transfer in distributed computing with applications to VLSI,Journal of the ACM, vol. 31, n. 1, pp. 150–162; January 1984.

J. E. Savage, “Area-time tradeoffs for matrix multiplication and related problems in VLSI models,”Journal of Computer System Science, vol. 22, n. 2, pp. 230–242; April 1981.

R. P. Brent and H. T. Kung, “The chip complexity of binary arithmetic,”Journal of the ACM, vol. 28, n. 3, pp. 521–534; My 1981.

F. T. Leighton, “Tight bounds on the complexity of parallel sorting,”Proc. 16th Annual ACM Symposium on Theory of Computing, Washington, D.C., pp. 71–80; April 1984. (AlsoIEEE Trans. on Comput.; April 1985.)

P. Duris, O. Sykora, C. Thompson, and I. Vrto, “A tight chip area lower bound for sorting,”Computers and Artificial Intelligence, to appear; 1985.

J. D. Ullman,Computational Aspects of VLSI, Computer Science Press, Rockville, MD, 1983.

C. D. Thompson and D. Angluin, “OnAT 2 lower bounds for sorting,”manuscript draff; March 1983.

A. Siegel, “Tight area bounds and provably goodAT 2 bounds for sorting circuits,” Tech. Report #122 Courant Institute, New York University; June 1984.

G. Bilardi,The Area-Time Complexity of Sorting, Ph.D. Thesis, Univ. of Illinois; December 1984.

G. Bilardi and F. P. Preparata, “An architecture for bitonic sorting with optimal VLSI performance,”IEEE Trans. Comp., vol. C-33, n. 7, pp. 640–651; July 1984.

G. Bilardi and F. P. Preparata, “A minimum area VLSI network forO(logN) time sorting,”Proc. 16th Annual ACM Symposium on Theory of Computing, Washington, D.C., pp. 64–70; April 1984. (AlsoIEEE Trans. on Comput., April 1985.)

G. Bilardi and F. P. Preparata, “The VLSI optimality of the AKS sorting network,”Information Processing Letters, vol. 20, n. 2, pp. 55–59, Feb. 1985.

G. Bilardi and F. P. Preparata, “The influence of key length on the area-time complexity of sorting,” I. C. A. L. P., Nauplion, Greece; July 1985.

R. Cole and A. Siegel, “Optimal VLSI circuits for sorting,” manuscript; 1985.

C. D. Thompson, “The VLSI complexity of sorting,”IEEE Trans. Comp., vol. C-32, n. 12, pp. 1171–1184; December 1983.

Author information

Authors and Affiliations

Additional information

Communicated by C. K. Wong.

This work was supported in part by the National Science Foundation ECS-84-10902, by an IBM predoctoral fellowship, and by the Joint Services Electronics Program under Contract N00014-84-C-0149. A preliminary version was presented at the 19th Conference on Information Sciences and Systems.

Rights and permissions

About this article

Cite this article

Bilardi, G., Preparata, F.P. Area-time lower-bound techniques with applications to sorting. Algorithmica 1, 65–91 (1986). https://doi.org/10.1007/BF01840437

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF01840437