Abstract

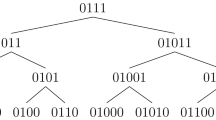

Parallel algorithms are examined for a number of fundamental computational problems. All algorithms have as a basic operation the addition ofk-bit integers. For each problem we present a solution in the form of a logical circuit for which the product of the computation time and number of gates used is smaller than that of the best previously known algorithm.

Zusammenfassung

Wir untersuchen parallele Algorithmen für eine Anzahl von grundlegenden Rechenproblemen. Alle Algorithmen besitzen als Grundoperation die Additionk-stelliger Binärzahlen. Für jedes Problem geben wir die Lösung in Form eines logischen Schaltkreises, für den das Produkt aus Rechenzeit und Anzahl der benutzten Gatter kleiner ist als bei den besten bisher bekannten Algorithmen.

Similar content being viewed by others

References

Akl, S. G.: Parallel Sorting Algorithms. Orlando, Florida: Academic Press 1985.

Baer, J.-L.: Computer Systems Architecture. Rockville, Maryland: Computer Science Press 1980.

Cooper, J., Akl, S. G.: Efficient selection on a binary tree. Information Processing Letters, Vol. 23, No. 3, October 1986.

Gonnet, G. H.: Handbook of Algorithms and Data Structures. Don Mills, Ontario: Addison-Wesley 1984.

Kuck, D. J.: The Structure of Computers and Computations, Vol. 1. Toronto: John Wiley & Sons 1978.

Stone, H. S., ed.: Introduction to Computer Architecture. Toronto: Science Research Associates 1980.

Ullman, J. D.: Computational Aspects of VLSI. Rockville, Maryland: Computer Science Press 1984.

Author information

Authors and Affiliations

Additional information

This work was supported by the Nutural Sciences and Engineering Research Council of Canada under grants A0282 and A3336.

Rights and permissions

About this article

Cite this article

Meijer, H., Akl, S.G. Bit serial addition trees and their applications. Computing 40, 9–17 (1988). https://doi.org/10.1007/BF02242186

Received:

Issue Date:

DOI: https://doi.org/10.1007/BF02242186

Categories and Subject Descriptors

- B.5.1 [Register-Transfer-Level Implementation] Design-Arithmetic and logic units

- B.6.1 [Logic Design]: Design styles-Parallel circuits

- F.2.0. [Analysis of Algorithms and Problem Complexity]: General